# LAMPIRAN

# LAMPIRAN A

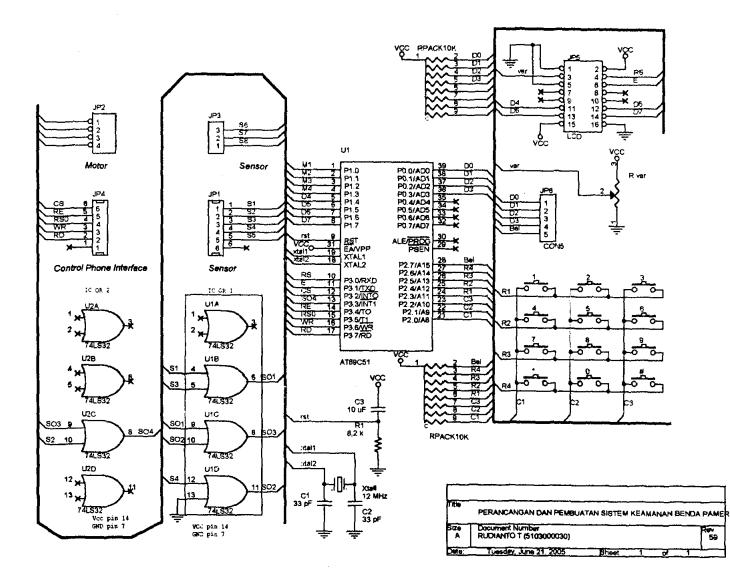

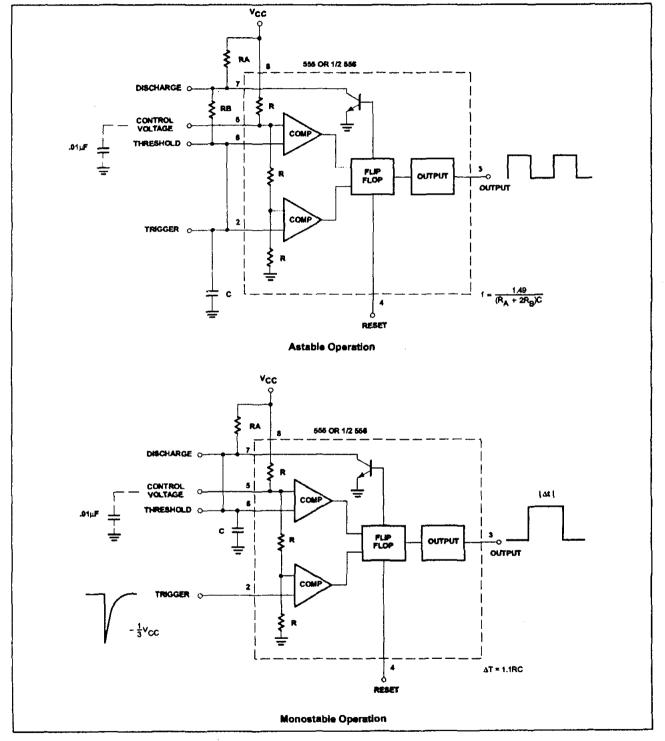

# SKEMA RANGKAIAN

1

•

•

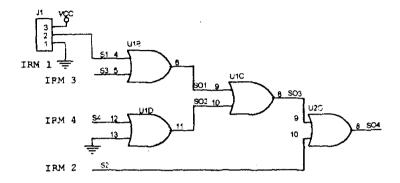

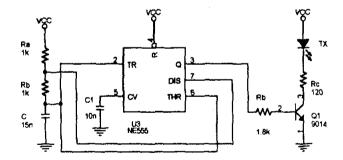

Rangkaian penerima infra merah

### Rangkaian pemancar infra merah

| tie  |                       |         |                     |

|------|-----------------------|---------|---------------------|

|      | RANGKAIAN SENSOR INFR | A MERAH |                     |

| Size | Document Number       |         | Røv                 |

|      | <doc></doc>           |         | <revcode></revcode> |

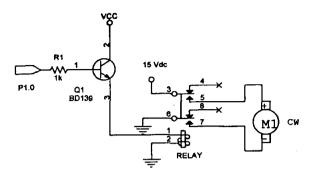

menurunkan tempat benda pamer

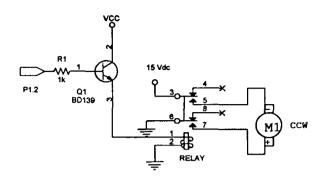

menaikkan tempat benda pamer

.

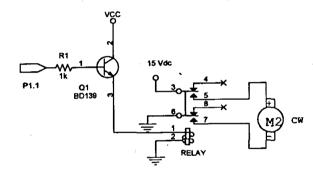

menutup benda pamer

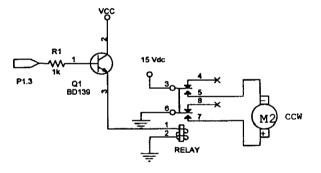

membuka penutup benda pamer

| itle  | RANGKAIAN DRIVER MOTOR D | c     |      |         |

|-------|--------------------------|-------|------|---------|

| Size  | Document Number          |       | <br> | <br>Rev |

| A     | RUDIANTO T (5103000030)  |       |      |         |

| Date: | Tuesday, June 21, 2005   | Sheet | <br> | <br>    |

.

•

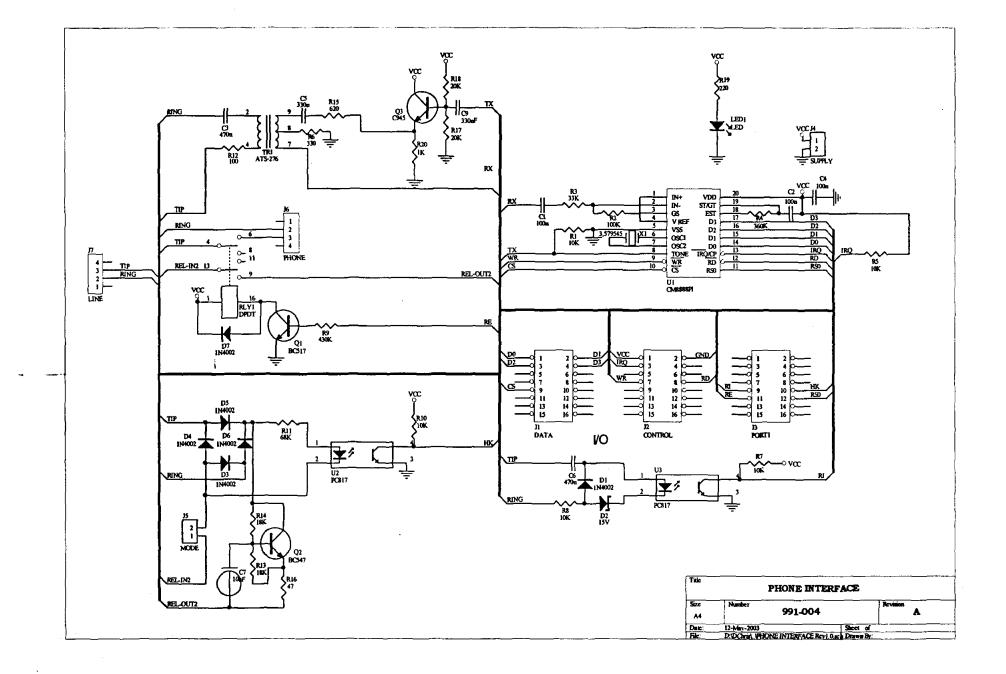

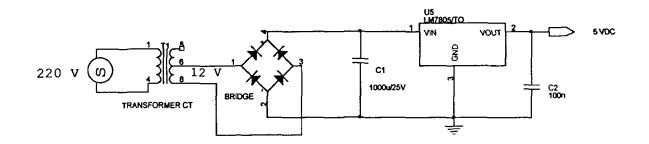

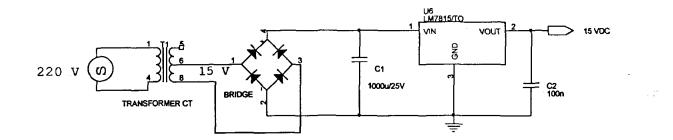

| Title     | RANGKAIAN POWER SUPPLY                     |       |   |    |   |                                               |       |

|-----------|--------------------------------------------|-------|---|----|---|-----------------------------------------------|-------|

| Size<br>A | Document Number<br>RUDIANTO T (5103000030) |       |   |    |   | Rev<br><revc< th=""><th>;ode&gt;</th></revc<> | ;ode> |

| Date:     | Tuesday, June 28, 2005                     | Sheet | 1 | of | 1 | <u> </u>                                      |       |

# LAMPIRAN B

# LISTING PROGRAM

$\geq \frac{2}{\lambda}$

|                                                                 | ju 70H                                                                                                                                                          |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS BI<br>E BI<br>CS8886 BI<br>RE BI                             | T P2.7<br>T P3.0<br>T P3.1<br>T P3.2<br>T P3.4<br>T P3.5                                                                                                        |

| FESAN1:DB 'INPESAN2:DB 'AGPESAN3:DB 'PESAN4:DB 'AGPESAN5:DB 'VE | HPUT PASSWORD ', OFH<br>HPUT TELF NO ', OFH<br>REE?1=NO 2=YES', OFH<br>->CHECKING<', OFH<br>LARM ACTIVATE ', OFH<br>RIFY PASSWORD', OFH<br>T PASS 1=Y 2=N', OFH |

| DSEG AT 30H<br>MODE: DS 1                                       |                                                                                                                                                                 |

| CSEG<br>;++++++++++++++++++++++++++++++++++++                   | +++++                                                                                                                                                           |

| RESET:                                                          |                                                                                                                                                                 |

| MOV P1,#0H                                                      | ; MATIKAN MOTOR DC                                                                                                                                              |

| MOV P2,#0H                                                      |                                                                                                                                                                 |

| MOV SP, #40H                                                    |                                                                                                                                                                 |

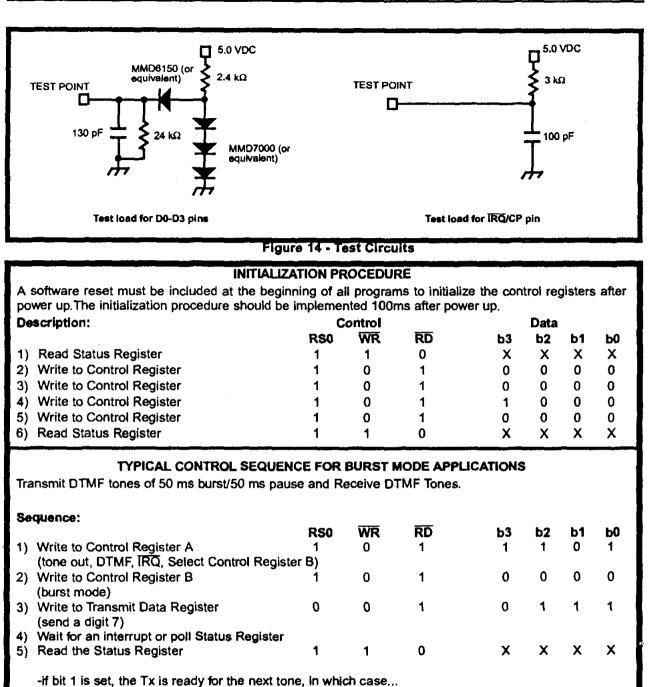

| LCALL RESET8888                                                 | ;RESET MT8888                                                                                                                                                   |

| MOV MODE, #DTMF                                                 | 1 ; PINDAH DATA ODH UNTUK                                                                                                                                       |

| LCALL INIT8888                                                  | INISIALISASI MT8888<br>;INISIALISASI MT8888                                                                                                                     |

| LCALL INIT LCD                                                  | , INTERNETORET MIG000                                                                                                                                           |

| LCALL PASSWORD                                                  |                                                                                                                                                                 |

| AJMF NOMOR                                                      |                                                                                                                                                                 |

|                                                                 |                                                                                                                                                                 |

1

\$MOD51

MT8888 DTMF1

DIGIT

PASS COMP

ORG 0000H AJMP RESET

.

EQU

EQU

EQU

EQU

EQU 0000H

0DH

31H

50H

60H

| ; PROSEDUR | PASSWORD         |                                         |

|------------|------------------|-----------------------------------------|

| PASSWORD:  |                  |                                         |

|            | A,#01H           | ; DISPLAY CLEAR                         |

|            | KIRIM PERINTAH   | , , , , , , , , , , , , , , , , , , , , |

|            | DPTR, #PESANO    | ;TAMPILKAN PESAN 0                      |

|            | KIRIMPESAN LCD   | ,                                       |

|            | А, #ОСОН         | ; BARIS 2 LCD AKTIF                     |

|            | KIRIM_PERINTAH   | ,                                       |

| MOV        | PASS, #51H       |                                         |

| CEK PASS:  |                  |                                         |

| MOV        | DIGIT,#00H       |                                         |

| ACALL      |                  | CEK PENEKANAN TOMBO                     |

| MOV        |                  |                                         |

| CJNE       | A, #00H, PASS1   |                                         |

| AJMP       | CEK_PASS         |                                         |

| PASS1:     |                  |                                         |

| CJNE       | A, #23H, PASS2   | ;TOMBOL # DITEKAN ?                     |

|            | R1, PASS         |                                         |

| MOV        | @R1,#'\$'        | ;ISI PASSWORD SELESA                    |

| RET        |                  |                                         |

| PASS2:     |                  |                                         |

|            | •                | ;TAMPILKAN * PADA LO                    |

|            | KIRIM_KARAKTER   | ;KIRIM KE LCD                           |

| MOV        | A, DIGIT         |                                         |

| SWAP       | А                |                                         |

|            | R1, PASS         |                                         |

|            | 0R1,A            |                                         |

| INC        | 50H              |                                         |

| AJMP       | CEK_PASS         |                                         |

| ;          |                  |                                         |

|            | R MASUKKAN NOMOR |                                         |

| NOMOR:     |                  |                                         |

|            | FIXED, #71H      |                                         |

| MOV        |                  | ;DISPLAY CLEAR                          |

|            | KIRIM PERINTAH   |                                         |

| MOV        | DPTR, #PESAN1    | ;TAMPILKAN PESAN 1                      |

|            | KIRIMPESAN_LCD   |                                         |

|            | А, #0СОН         | ;BARIS 2 LCD AKTIF                      |

| ACALL      | KIRIM PERINTAH   |                                         |

| CEK_NO:<br>MOV<br>ACALL<br>MOV<br>CJNE<br>AJMP | DIGIT, #00H<br>SCAN_KEY<br>A, DIGIT<br>A, #00H, CEK1<br>CEK_NO      |                                                |

|------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------|

| CEK1:<br>CJNE<br>MOV<br>MOV<br>AJMP            | R1, FIXED                                                           | ;TOMBOL # DITEKAN?<br>;ISI NOMOR SELESAI       |

| ACALL<br>MOV                                   | A,DIGIT<br>KIRIM_KARAKTER<br>R1,FIXED<br>@R1,DIGIT<br>70H<br>CEK_NO | ;ISI AKUMULATOR=ISI DIGIT<br>;TAMPILKAN DI LCD |

| ;; CONFIRM                                     | PHONE NUMBER                                                        |                                                |

| ACALL<br>MOV                                   | A,#80H<br>KIRIM_PERINTAH<br>DPTR,#PESAN2<br>KIRIMPESAN_LCD          | ;AKTIFKAN BARIS 1 LCD<br>;TAMPILKAN PESAN 2    |

| TANYA1:<br>MOV<br>ACALL<br>MOV<br>CJNE<br>AJMP | DIGIT, #00H<br>SCAN_KEY<br>A, DIGIT<br>A, #31H, TANYA2<br>NOMOR     | ;1 DITEKAN ?<br>;UBAH NOMOR TELEPON            |

;2 DITEKAN?

; DISPLAY CLEAR

;TAMPILKAN PESAN 3

TANYA2: CJNE

PROSES:

MOV ACALL

MOV

ACALL

A, #32H, TANYA1

KIRIM PERINTAH

KIRIMPESAN\_LCD

DPTR, #PESAN3

A,#01H

.

| SETB       | P3.3           | ; p3.3 = INPUT SENSOR    |

|------------|----------------|--------------------------|

| NOP        |                | ,                        |

| NOP        |                |                          |

| 1101       |                |                          |

|            |                |                          |

| ;RED AL    | .ert<br>       |                          |

|            |                | ;SENSOR TERHALANG?       |

| RED ALE    | RT:            |                          |

|            | A,#01H         | ;CLEAR LCD               |

|            | KIRIM PERINTAH |                          |

| MOV        | DPTR, #PESAN4  |                          |

| ACALL      | KIRIMPESAN LCD |                          |

| SETB       | BUZZ           | ;BUZZER ON               |

| SETB       | P1.0           | ; TEMPAT BARANG TURUN    |

|            | DELAY2S        | ,                        |

| ACALL      |                |                          |

|            | P1.0           |                          |

|            | P1.1           | ;TUTUP DAERAH UTAMA      |

|            | DELAY 3S       | ,                        |

|            | DELAY500MS     |                          |

| CLR        | P1.1           |                          |

|            |                |                          |

|            | G NUMBER       |                          |

| ;          |                |                          |

| SETB       |                | ;ANGKAT GAGANG TELEPON   |

|            | DELAY_3S       |                          |

| ACALL      |                | ; MELAKUKAN DTMF DIALING |

| ACALL      | DELAY2S        |                          |

|            | DELAY2S        |                          |

|            | DELAY2S        |                          |

| ACALL      |                |                          |

| ACALL      | DELAY2S        |                          |

| CLR        | BUZZ           | ;BUZZER OFF              |

| CLR        | RE             | ;TUTUP GAGANG            |

| ;          | _ ~            |                          |

| ;CONFIR    | M PASSWORD     |                          |

| ;<br>CONF: |                |                          |

|            | A,#01H         | ;DISPLAY CLEAR           |

| ACALL      |                | INTOLIMI CHEWK           |

| MOV        | DPTR, #PESAN5  | ;TAMPILKAN PESAN 5       |

| ACALL      |                | LUTT TRUTH L POWLY O     |

| ИСИПЛ      | VIVINEDONN TOD |                          |

|            |                |                          |

4

.

| ACALL        | A,#0COH<br>KIRIM_PERINTAH<br>COMP,#61H | ;BARIS 2 LCD AKTIF                     |

|--------------|----------------------------------------|----------------------------------------|

| ACALL<br>MOV | DIGIT,#00H<br>SCAN_KEY                 |                                        |

| MOV<br>MOV   | R1,COMP<br>@R1,#'\$'                   | ;TOMBOL # DITEKAN?                     |

| AJMP         | VER                                    | ; PERIKSA PASSWORD                     |

| ACALL        | A,#2AH<br>KIRIM_KARAKTER<br>A,DIGIT    | ;TAMPILKAN * PADA LCD                  |

| SWAP         | A                                      |                                        |

|              | R1, COMP                               |                                        |

|              | 0R1, A                                 |                                        |

| INC          | 60H                                    |                                        |

| AJMP         | CEK_CONF                               |                                        |

| •            |                                        |                                        |

| ; PASSWORD   |                                        |                                        |

| ;            |                                        |                                        |

| VER:         |                                        |                                        |

|              | PASS,#51H                              |                                        |

|              | COMP,#61H                              |                                        |

|              |                                        |                                        |

| CEK_VER:     |                                        |                                        |

| MOV          | R1, COMP                               | ;COMP->A                               |

| MOV          | A, 0R1                                 |                                        |

| MOV          | R1, PASS                               | ;PASS->B                               |

| MOV          | B, @R1                                 |                                        |

| CJNE         | A, B, CONF                             | ;A = B ?                               |

| INC          | 50H                                    | ;AMBIL DATA BERIKUTNYA                 |

| INC          | 60H                                    | ;AMBIL DATA BERIKUTNYA                 |

| CJNE         | A,#'\$',CEK VER                        | ; DATA DI COMP HABIS?                  |

| MOV          | A, B                                   |                                        |

| CJNE         | A, #'\$', CONF                         | ;DATA DI PASS HABIS?                   |

| + + - ·      |                                        | · ···································· |

•

.

0

;CHANGE PASSWORD CHANGE: MOV A,#01H ;CLEAR LCD KIRIM PERINTAH ACALL MOV DPTR, #PESAN6 ACALL KIRIMPESAN LCD CH1: MOV DIGIT,#00H ACALL SCAN KEY MOV A, DIGIT CJNE A,#31H,CH2 AJMP CH3 CH2: CJNE A,#32H,CH1 AJMP COMPLETE CH3: LCALL PASSWORD ; PASSWORD CHANGE COMPLETE ; ------COMPLETE: P1.3 SETB ; BUKA DAERAH UTAMA DELAY 3S ACALL CLR P1.3 SETB P1.2 ;TEMPAT BARANG NAIK ACALL DELAY2S DELAY2S ACALL DELAY500MS ACALL CLR P1.2 AJMP PROSES ;KEMBALI PERIKSA SENSOR ;WRITE DTMF ; DIAMBIL DARI TUTORIAL PHONE INTERFACE ;-----WRITEDTME: DEH PUSH PUSH DPL CLR RSOX ;RS0=0

MOV DPTR, #MT8888 MOVX ODPTR, A POP DPL POP DPH RET ;READ STATUS MT8888 ; DIAMBIL DARI TUTORIAL PHONE INTERFACE READSTAT: PUSH DPH DPL PUSH SETB RSOX ;RS0=1 MOV DPTR, #MT8888 A, @DPTR MOVX RSOX CLR ;RS0=0 POP DPL POP DPH RET ;WRITE CONTROL REGISTER ; DIAMBIL DARI TUTORIAL PHONE INTERFACE WRITECR: DPH PUSH PUSH DPL SETB RSOX ;RS0=1 DPTR,#MT8888 MOV ODPTR, A MOVX RSOX ;RS0=0 CLR POP DPL POP DPH RET ;RESET MT8888 ; DIAMBIL DARI TUTORIAL PHONE INTERFACE RESET8888: ACC PUSH CLR CS8888 RE CLR ACALL READSTAT A,#00H MOV ACALL WRITECR

•

| ACALL | WRITECR  |

|-------|----------|

| MOV   | A,#08H   |

| ACALL | WRITECR  |

| MOV   | A,#00H   |

| ACALL | WRITECR  |

| ACALL | READSTAT |

| POP   | ACC      |

| RET   |          |

;-----;INIT MT8888

; DIAMBIL DARI TUTORIAL PHONE INTERFACE INIT8888: PUSH ACC DPH PUSH DFL FUSH MOV A, MODE ACALL WRITECR JNB ACC.3, EO INIT8888 SWAP А ACALL WRITECR

### EO\_INIT8888:

| POP | DPL |

|-----|-----|

| POP | DPH |

| POP | ACC |

| RET |     |

; DTMF DIALING NUMBER ; DIAMBIL DARI TUTORIAL PHONE INTERFACE ; DENGAN MODIFIKASI PADA PROSES PENGIRIMAN DATA ;------

$\mathbf{C}$

DTMFDIALING: MOV FIXED,#71H

#### NXTNUMBER:

| MOV                 | R1,FIXED     |

|---------------------|--------------|

| MOV                 | A, @R1       |

| CJNE<br>R <b>ET</b> | A,#'\$',DIAL |

| DIAL:               |              |

| INC  | 70H             |

|------|-----------------|

| CJNE | A, #30H, DIAL19 |

DIALO: MOV A,#OAH ACALL WRITEDTMF UP1: ACALL READSTAT JNB ACC.1,UP1 AJMP NXTNUMBER DIAL19: ACALL WRITEDTMF UP2: ACALL READSTAT JNB ACC.1, UP2 AJMP NXTNUMBER PROSEDUR SCAN KEYPAD ; SCAN KEY: ;SAVE LOGIC P2.7 KOLOM1: PUSH H08 A, #7EH MOV MOV P2,A DELAY 15MS ACALL MOV A, P2 ACALL DELAY 15MS CJNE A, #7EH, ANGKA1 AJMP KOLOM2 ANGKA1: CJNE A, #76H, ANGKA4 MOV A,#31H MOV DIGIT,A DELAY 065S ACALL AJMP OUT KEY ANGKA4: CJNE A, #6EH, ANGKA7 MOV A,#34H MOV DIGIT, A ACALL DELAY 065S AJMP OUT KEY ANGKA7: A, #5EH, ANGKA11 CJNE A,#37H MOV DIGIT,A MOV DELAY 065S ACALL OUT KEY AJMP

9

| ANGKA11: | MOV<br>MOV<br>ACALL<br>AJMP                         | A,#2AH<br>DIGIT,A<br>DELAY_065S<br>OUT_KEY                                         |

|----------|-----------------------------------------------------|------------------------------------------------------------------------------------|

| KOLOM2:  | MOV<br>MOV<br>ACALL<br>MOV<br>ACALL<br>CJNE<br>AJMP | A, #7DH<br>P2, A<br>DELAY_15MS<br>A, P2<br>DELAY_15MS<br>A, #7DH, ANGKA2<br>KOLOM3 |

| ANGKA2:  | CJNE<br>MOV<br>MOV<br>ACALL<br>AJMP                 | A, #75H, ANGKA5<br>A, #32H<br>DIGIT, A<br>DELAY_065S<br>OUT_KEY                    |

| ANGKA5:  | CJNE<br>MOV<br>MOV<br>ACALL<br>AJMP                 | A, #6DH, ANGKA8<br>A, #35H<br>DIGIT, A<br>DELAY_065S<br>OUT_KEY                    |

| ANGKA8:  | CJNE<br>MOV<br>MOV<br>ACALL<br>AJMP                 | A, #5DH, ANGKAO<br>A, #38H<br>DIGIT, A<br>DELAY_065S<br>OUT_KEY                    |

| ANGKA0:  | MOV<br>MOV<br>ACALL<br>AJMP                         | A,#30H<br>DIGIT,A<br>DELAY_065S<br>OUT_KEY                                         |

| KOLOM3:  | ACALL<br>MOV<br>ACALL<br>CJNE                       | A, #7BH<br>P2,A<br>DELAY_15MS<br>A, P2<br>DELAY_15MS<br>A, #7BH, ANGKA3<br>OUT_KEY |

10

•

•

|                         | ~ ~ ~ ~ ~ ~ |                        | ~                            |

|-------------------------|-------------|------------------------|------------------------------|

| ANGKA3:                 | CJNE        |                        | 6                            |

|                         | MOV         | •                      |                              |

|                         | MOV         | ,                      |                              |

|                         | ACALL       |                        |                              |

|                         | AJMP        | OUT_KEY                |                              |

| ANGKA6:                 | CJNE        | A,#6BH,ANGKA           | 9                            |

|                         | MOV         | A,#36H                 |                              |

|                         | MOV         |                        |                              |

|                         | ACALL       | -                      |                              |

|                         | AJMP        |                        |                              |

| ANGKA9:                 | CJNE        | A,#5BH,ANGKA           | 1 2                          |

| Midiui).                | MOV         | A, #39H                |                              |

|                         | MOV         | DIGIT,A                |                              |

|                         | ACALL       | •                      |                              |

|                         | AJMP        | OUT KEY                |                              |

|                         | num         |                        |                              |

| ANGKA12:                | MOV         | A,#23H                 |                              |

|                         | MOV         |                        |                              |

|                         | ACALL       | •                      |                              |

|                         | AJMP        | OUT KEY                |                              |

|                         |             |                        |                              |

| OUT_KEY:                | POP 8       | ОН                     |                              |

|                         | RET         |                        |                              |

| • • • • • • • • • • • • | ·+++++++    | ╋ <b>┽╅╋┾┽</b> ╪╪┽╪╋┿┿ | ┢┽┼ <b>┽</b> ┼┽┽┽┿┿┿┽┼┼┾     |

| -                       |             | ISIALISASI LCI         |                              |

| •                       |             |                        | <b>⊦</b> ∔ <b>∔┾┿┿┿┿┿┿┿┿</b> |

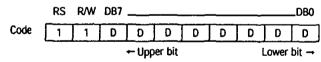

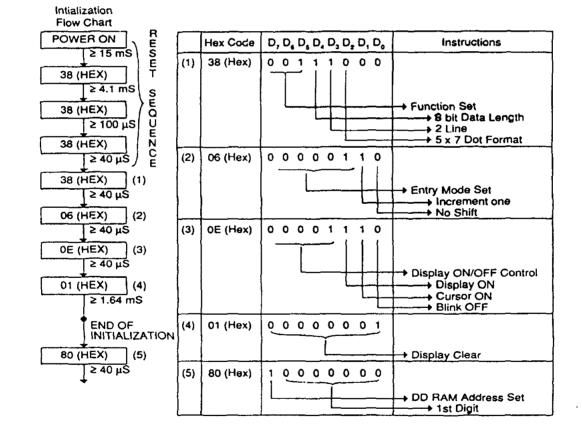

| INIT LCD:               |             |                        |                              |

| MOV                     | A.#30H      |                        |                              |

| ACALL                   |             |                        |                              |

|                         | A,#30H      |                        |                              |

|                         |             | PERINTAH               |                              |

| MOV                     | A, #30H     |                        |                              |

|                         |             | PERINTAH               |                              |

| ACALL                   |             |                        |                              |

| MOV                     | A, #20H     |                        |                              |

| ACALL                   |             | PERINTAH               | - EUNCETON OF                |

| MOV                     | A,#28H      |                        | ;FUNCTION SET                |

| ACALL                   |             | PERINTAH               |                              |

| MOV                     | A,#06H      |                        | ;ENTRY MODE SET              |

| ACALL                   | _           | PERINTAH               | DIODINY ON                   |

| MOV                     | A,#0CH      |                        | ;DISPLAY ON                  |

| ACALL                   |             | PERINTAH               |                              |

| VOM                     | A,#01H      |                        | ;DISPLAY CLEAR               |

| ACALL                   | KIRIM_      | PERINTAII              |                              |

| RET                     |             |                        |                              |

|                         |             |                        |                              |

11

.

•

#### KIRIM\_PERINTAH: CLR RS ACALL KIRIM\_DATALCD SWAP A ACALL KIRIM\_DATALCD ACALL DELAY\_4MS RET

#### KIRIM\_DATALCD:

| PUSH | ACC     |

|------|---------|

| ANL  | A,#0F0H |

| MOV  | R2,A    |

| MOV  | A, P1   |

| ANL  | A,#0FH  |

| ORL  | A, R2   |

| MOV  | P1,A    |

| SETB | E       |

| CLR  | E       |

| POP  | ACC     |

| RET  |         |

#### KIRIMPESAN LCD:

#### LOOPKIRIMPESAN:

| MOV  | A,#00H             |

|------|--------------------|

| MOVC | A, @A+DFTR         |

| CJNE | A, #OFH, KIRIM LCD |

| RET  | _                  |

KIRIM\_LCD: ACALL KIRIM\_KARAKTER INC DPTR AJMP LOOPKIRIMPESAN

KIRIM\_KARAKTER: SETB RS ACALL KIRIM\_DATALCD SWAP A ACALL KIRIM\_DATALCD ACALL DELAY\_50US

#### RET

$\odot$

.

PROSEDUR DELAY ; **┆**┝┶┶┿┿┿┿┿┿┿┿┿┿┿┿┿┿┿┿┿┿┿┿┿┿ DELAY2S: PUSH 05H PUSH 06H PUSH 07H MOV R5,#20 LDEL2S 2: MOV R6,#200 LDEL2S\_1: MOV R7, #250 DJNZ R7,\$ DJNZ R6, LDEL2S 1 DJNZ R5, LDEL2S 2 POP 07H POP 06H POP 05H RET DELAY 4MS: MOV R0, #0FFH MOV R1, #10H DELAY 4MS1: DJNZ RO, DELAY 4MS1 DJNZ R1, DELAY 4MS1 RET DELAY 50US: MOV RO,#12H R1,#02H MOV DELAY 50US1: DJNZ RO, DELAY\_50US1 DJNZ R1, DELAY 50US1 RET DELAY 15MS: MOV RO, #OFFH MOV R1,#2FH DELAY 15MS1: DJNZ RO, DELAY 15MS1 DJNZ R1, DELAY 15MS1 RET DELAY500MS: MOV R2,#04H MOV RO, #OFFH D5: MOV R1, #0FEH D51: DJNZ R1,\$ DJNZ RO, D51 DJNZ R2, D5 NOP RET

| DELAY_1S:<br>LOP:<br>LOP1:<br>HERE: | MOV<br>MOV<br>DJNZ<br>DJNZ | R1,#0<br>R2,#3             | 68Н<br>32Н<br>ЭР1                                                   |  |

|-------------------------------------|----------------------------|----------------------------|---------------------------------------------------------------------|--|

| DELAY_3S:                           |                            |                            | DELAY_1S<br>DELAY_1S<br>DELAY_1S                                    |  |

| DELAY_200N<br>AGAIN:                | AC<br>DC                   | CALL                       | R7,#14<br>DELAY_15MS<br>R7,AGAIN                                    |  |

| DELAY_0655<br>TNDA1:<br>TNDA2:      | 5:                         | MOV<br>MOV<br>DJNZ<br>DJNZ | R0, #5H<br>R1, #0FFH<br>R2, #0H<br>R2, \$<br>R1, TNDA2<br>R0, TNDA1 |  |

RET

;DELAY 0,65S

.

•

END

,

# LAMPIRAN C

# DATA SHEET

.

### Features

- Compatible with MCS-51<sup>™</sup> Products

- 4K Bytes of in-System Reprogrammable Flash Memory – Endurance: 1,000 Write/Erase Cycles

- · Fully Static Operation: 0 Hz to 24 MHz

- Three-Level Program Memory Lock

- 128 x 8-Bit Internal RAM

- 32 Programmable I/O Lines

- Two 16-Bit Timer/Counters

- Six Interrupt Sources

- Programmable Serial Channel

- Low Power Idle and Power Down Modes

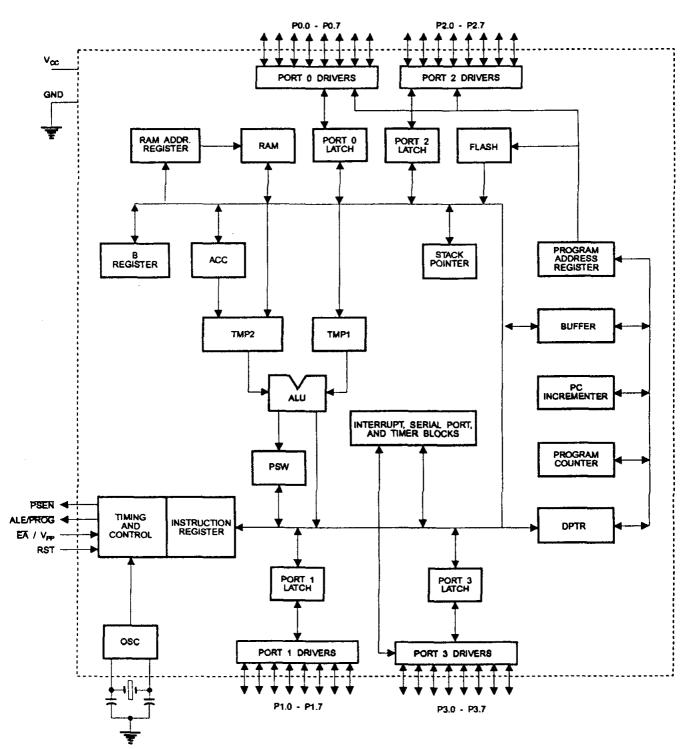

# Description

The AT89C51 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of Flash Programmable and Erasable Read Only Memory (PEROM). The device is manufactured using Atmel's high density nonvolatile memory technology and is compatible with the industry standard MCS-51<sup>™</sup> instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C51 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications. *(continued)*

#### PDIP Pin Configurations P1.0 C P1.1 C P1.2 C P1.3 C P1.4 C P1.5 C P1.5 C P1.7 C RST C P3.0 C P3.1 C JVCC P0.0 P0.1 P0.2 P0.3 P0.4 (AD0) (AD1) (AD2) 2345 38 37 (AD3) (AD4) 36 35 6 P0.5 (AD5) P0.6 (AD6) P0.7 (AD7) 34 33 8 9 32 P3.0 P3.1 31 30 EKIVPP (RXD) POFP/TOFP DALE/PROG DPSEN DP2.7 (A15) DP2.6 (A14) (TXD) (INTO) (INTT) C 11 12 13 Р3 Р3 29 28 . 2 . 3 (T0) (T1) (WR) 27 28 25 24 23 P3 14 5 P2.8 (413) INDEX РĴ . 5 15 P2.4 P2.3 P2.2 P2.1 ) P3.6 [] ) P3.7 [] XTAL2 [] XTAL1 [] 16 17 (A12) (RD) (A11) 18 (A10) 19 22 P1.5 C P1.6 C P1.6 C RST C (RXD) P3.0 C (TXD) P3.1 C (TXD) P3.1 C (TXT) P3.2 C (TT) P3.3 C (TT) P3.5 C P2.0 P0.4 (AD4) GND C 20 21 (88) P0.5 (AD5) P0.6 (AD6) P0.7 (AD7) 32 31 30 29 PLCC 30 P0.7 (AD7) 20 EA/VPP 28 NC 27 ALE/PROG 26 PSEN 25 P2.7 (A15) 24 ALE/PROG (A02) AD0 INDEX U V V 04 10 24 23 EP2.6 (A14) 2<sup>1 3</sup>14<sup>1 5</sup>18<sup>1 7</sup>18<sup>1 9</sup>20<sup>2 1</sup> (AD4) PO.5 (AD5) PO.8 (AD8) PO.7 (AD7) **R\$1** (RXD) **SEXIVPP** 3 NC NC (TXD) P3.10 P3.20 ALE/PROG PSEN (ÎNTO) UNTT 3P2.7 P3.3 C (A15 (T0) (T1) (A14) (A13)

8-Bit Microcontroller with 4K Bytes Flash

# AT89C51

0265F-A-12/97

AIMEL

## lock Diagram

AT89C51

4-30

The AT89C51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The Power Down Mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset.

### **Pin Description**

V<sub>CC</sub> Supply voltage.

GND Ground.

#### Port 0

Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs.

Port 0 may also be configured to be the multiplexed loworder address/data bus during accesses to external program and data memory. In this mode P0 has internal pullups.

Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program ventication. External pullups are required during program ventication.

#### Port 1

Port 1 is an 8-bit bidirectional I/O port with internal pullups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current ( $I_{IL}$ ) because of the internal pullups.

Port 1 also receives the low-order address bytes during Flash programming and verification.

#### Port 2

Port 2 is an 8-bit bidirectional I/O port with internal pullups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current ( $I_{1L}$ ) because of the internal pullups.

Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application it uses strong internal pullups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.

Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.

#### Port 3

Port 3 is an 8-bit bidirectional I/O port with internal pullups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current ( $I_{IL}$ ) because of the pullups.

Port 3 also serves the functions of various special features of the AT89C51 as listed below:

| Port Pin | Alternate Functions                    |  |  |

|----------|----------------------------------------|--|--|

| P3.0     | RXD (serial input port)                |  |  |

| P3.1     | TXD (serial output port)               |  |  |

| P3.2     | INTO (external Interrupt 0)            |  |  |

| P3.3     | INT1 (external interrupt 1)            |  |  |

| P3.4     | T0 (timer 0 external input)            |  |  |

| P3.5     | T1 (timer 1 external input)            |  |  |

| P3.6     | WR (external data memory write strobe) |  |  |

| P3.7     | RD (external data memory read strobe)  |  |  |

Port 3 also receives some control signals for Flash programming and verification.

#### RST

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device.

#### ALE/PROG

Address Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.

In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.

If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.

#### PSEN

Program Store Enable is the read strobe to external program memory.

When the AT89C51 is executing code from external program memory, PSEN is activated twice each machine

cycle, except that two PSEN activations are skipped during each access to external data memory.

#### EA/V<sub>PP</sub>

External Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset.

$\overline{\text{EA}}$  should be strapped to  $V_{CC}$  for internal program executions.

This pin also receives the 12-volt programming enable voltage ( $V_{PP}$ ) during Flash programming, for parts that require 12-volt  $V_{PP}$ .

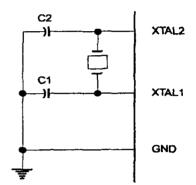

#### XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

#### XTAL2

Output from the inverting oscillator amplifier.

### **Oscillator Characteristics**

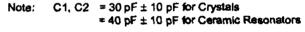

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

# Idle Mode

In idle mode, the CPU puts itself to sleep while all the onchip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.

### Status of External Pins During Idle and Power Down Modes

AT89C51

| Mode       | Program Memory | ALE | PSEN | PORTO | PORT1 | PORT2   | PORT3 |

|------------|----------------|-----|------|-------|-------|---------|-------|

| Idie       | Internal       | 1   | 1    | Data  | Data  | Data    | Data  |

| ldie       | External       | 1   | 1    | Float | Data  | Address | Data  |

| Power Down | internal       | 0   | 0    | Deta  | Data  | Data    | Data  |

| Power Down | External       | 0   | 0    | Float | Data  | Data    | Data  |

It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

Figure 1. Oscillator Connections

Figure 2. External Clock Drive Configuration

### **Power Down Mode**

In the power down mode the oscillator is stopped, and the instruction that invokes power down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the power down mode is terminated. The only exit from power down is a hardware reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before  $V_{CC}$  is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.

## **Program Memory Lock Bits**

On the chip are three lock bits which can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in the table below:

When lock bit 1 is programmed, the logic level at the  $\overline{EA}$  pin is sampled and latched during reset. If the device is powered up without a reset, the latch initializes to a random value, and holds that value until reset is activated. It is necessary that the latched value of  $\overline{EA}$  be in agreement with the current logic level at that pin in order for the device to function property.

# Lock Bit Protection Modes

|   | Program | Lock Bits | 8   | Protection Type                                                                                                                                                                                                 |

|---|---------|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | LB1     | LB2       | LB3 |                                                                                                                                                                                                                 |

| 1 | U       | U         | U   | No program lock features.                                                                                                                                                                                       |

| 2 | P       | U         | U   | MOVC instructions executed from external program memory are disabled from fetching code<br>bytes from internal memory, EA is sampled and latched on reset, and further programming of the<br>Flash is disabled. |

| 3 | Р       | Р         | U   | Same as mode 2, also verify is disabled.                                                                                                                                                                        |

| 4 | Р       | Р         | Р   | Same as mode 3, also external execution is disabled.                                                                                                                                                            |

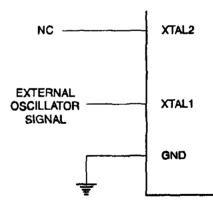

## **Programming the Flash**

The AT89C51 is normally shipped with the on-chip Flash memory array in the erased state (that is, contents = FFH) and ready to be programmed. The programming interface accepts either a high-voltage (12-volt) or a low-voltage ( $V_{CC}$ ) program enable signal. The low voltage programming mode provides a convenient way to program the AT89C51 inside the user's system, while the high-voltage programming mode is compatible with conventional third party Flash or EPROM programmers.

The AT89C51 is shipped with either the high-voltage or low-voltage programming mode enabled. The respective top-side marking and device signature codes are listed in the following table.

|               | V <sub>PP</sub> = 12V | V <sub>PP</sub> = 5V |

|---------------|-----------------------|----------------------|

| Top-Side Mark | AT89C51               | AT89C51<br>xxxx-5    |

|               | уумж                  | yyww                 |

| Signature     | (030H)=1EH            | (030H)=1EH           |

|               | (031H)=51H            | (031H)≂51H           |

|               | (032H)=FFH            | (032H)=05H           |

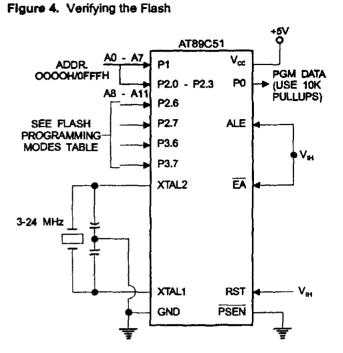

The AT89C51 code memory array is programmed byte-bybyte in either programming mode. To program any nonblank byte in the on-chip Flash Memory, the entire memory must be erased using the Chip Erase Mode. **Programming Algorithm:** Before programming the AT89C51, the address, data and control signals should be set up according to the Flash programming mode table and Figures 3 and 4. To program the AT89C51, take the following steps.

- 1. Input the desired memory location on the address lines.

- 2. Input the appropriate data byte on the data lines.

- 3. Activate the correct combination of control signals.

- 4. Raise EAV<sub>PP</sub> to 12V for the high-voltage programming mode.

- Pulse ALE/PROG once to program a byte in the Flash array or the lock bits. The byte-write cycle is self-timed and typically takes no more than 1.5 ms. Repeat steps 1 through 5, changing the address and data for the entire array or until the end of the object file is reached.

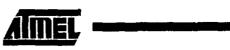

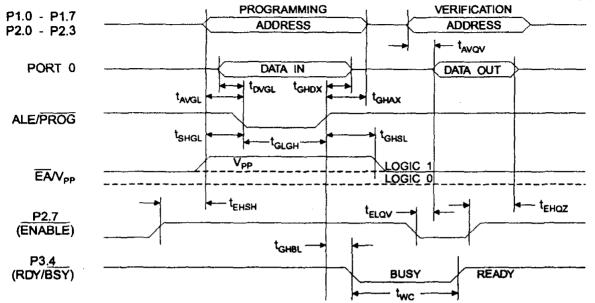

Data Polling: The AT89C51 features Data Polling to Indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written datum on PO.7. Once the write cycle

has been completed, true data are valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.

**Ready/Busy:** The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.4 is pulled low after ALE goes high during programming to indicate BUSY. P3.4 is pulled high again when programming is done to indicate READY.

**Program Verify:** If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. The lock bits cannot be verified directly. Verification of the lock bits is achieved by observing that their features are enabled.

Chip Erase: The entire Flash array is erased electrically by using the proper combination of control signals and by holding ALE/PROG low for 10 ms. The code array is written with all "1"s. The chip erase operation must be executed before the code memory can be re-programmed.

**Reading the Signature Bytes:** The signature bytes are read by the same procedure as a normal verification of locations 030H,

031H, and 032H, except that P3.6 and P3.7 must be pulled to a logic low. The values returned are as follows.

(030H) = 1EH indicates manufactured by Atmel (031H) = 51H indicates 89C51 (032H) = FFH indicates 12V programming (032H) = 05H indicates 5V programming

### **Programming Interface**

Every code byte in the Flash array can be written and the entire array can be erased by using the appropriate combination of control signals. The write operation cycle is selftimed and once initiated, will automatically time itself to completion.

All major programming vendors offer worldwide support for the Atmel microcontroller series. Please contact your local programming vendor for the appropriate software revision.

| Mode                |         | RST | PSEN | ALE/PROG | EA/Vpp | P2.6 | P2.7 | P3.6 | P3.7 |

|---------------------|---------|-----|------|----------|--------|------|------|------|------|

| Write Code Data     |         | Н   | L    | ~~       | H/12V  | L    | н    | н    | н    |

| Read Code Data      |         | н   | L    | Н        | н      | L    | L    | н    | н    |

| Write Lock          | Bit - 1 | н   | L    | $\sim$   | H/12V  | н    | н    | н    | н    |

|                     | Bit - 2 | н   | L    | ~~       | H/12V  | н    | н    | L    | L    |

|                     | Bit - 3 | н   | L    | ~~       | H/12V  | н    | L    | н    | L    |

| Chip Erase          |         | н   | L    | (1)      | H/12V  | н    | L    | L    | L    |

| Read Signature Byte |         | н   | L    | н        | н      | L    | L    | L    | L    |

### **Flash Programming Modes**

Note: 1. Chip Erase requires a 10-ms PROG pulse.

AT89C51

## **Flash Programming and Verification Characteristics**

$T_A = 0^{\circ}C$  to 70°C,  $V_{CC} = 5.0 \pm 10\%$

| Symbol                         | Parameter                       | Min                 | Max                 | Units |  |

|--------------------------------|---------------------------------|---------------------|---------------------|-------|--|

| V <sub>PP</sub> <sup>(1)</sup> | Programming Enable Voltage      | 11.5                | 12.5                | v     |  |

| Ipp <sup>(1)</sup>             | Programming Enable Current      |                     | 1.0                 | mA    |  |

| 1ACLCL                         | Oscillator Frequency            | 3                   | 24                  | MHz   |  |

| tAVGL                          | Address Setup to PROG Low       | 48t <sub>CLCL</sub> |                     |       |  |

| <sup>t</sup> GHAX              | Address Hold After PROG         | 48t <sub>CLCL</sub> |                     |       |  |

| 1 DVGL                         | Data Setup to PROG Low          | 48t <sub>CLCL</sub> |                     |       |  |

| <sup>t</sup> GHDX              | Data Hold After PROG            | 48t <sub>CLCL</sub> |                     |       |  |

| t <sub>EHSH</sub>              | P2.7 (ENABLE) High to VPP       | 48t <sub>CLCL</sub> |                     |       |  |

| tSHGL                          | VPP Setup to PROG Low           | 10                  |                     | μs    |  |

| tGHSL <sup>(1)</sup>           | V <sub>PP</sub> Hold After PROG | 10                  |                     | μs    |  |

| <sup>t</sup> GLGH              | PROG Width                      | 1                   | 110                 | μs    |  |

| t <sub>AVQV</sub>              | Address to Data Valid           |                     | 48t <sub>CLCL</sub> |       |  |

| <sup>1</sup> ELQV              | ENABLE Low to Data Valid        |                     | 48t <sub>CLCL</sub> |       |  |

| t <sub>EHQZ</sub>              | Data Float After ENABLE         | 0                   | 48t <sub>CLCL</sub> |       |  |

| <sup>1</sup> GHBL              | PROG High to BUSY Low           |                     | 1.0                 | μs    |  |

| WC .                           | Byte Write Cycle Time           |                     | 2.0                 | ms    |  |

Note: 1. Only used in 12-volt programming mode.

# Flash Programming and Verification Waveforms - High Voltage Mode (V<sub>PP</sub> = 12V)

Flash Programming and Verification Waveforms - Low Voltage Mode ( $V_{PP} = 5V$ )

AT89C51

4-36

# **Absolute Maximum Ratings\***

| Operating Temperature                        | 55°C to +125°C |

|----------------------------------------------|----------------|

| Storage Temperature                          | 65°C to +150°C |

| Voltage on Any Pin<br>with Respect to Ground | 1.0V to +7.0V  |

| Maximum Operating Voltage                    | 6.6V           |

| DC Output Current                            | 15.0 mA        |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **DC Characteristics**

$T_A = -40^{\circ}C$  to 85°C,  $V_{CC} = 5.0V \pm 20\%$  (unless otherwise noted)

| Symbol           | Parameter                                                | Condition                                             | Min                       | Max                       | Units      |

|------------------|----------------------------------------------------------|-------------------------------------------------------|---------------------------|---------------------------|------------|

| VIL              | Input Low Voltage                                        | (Except EA)                                           | -0.5                      | 0.2 V <sub>CC</sub> - 0.1 | v          |

| V <sub>IL1</sub> | Input Low Voltage (EA)                                   |                                                       | -0.5                      | 0.2 V <sub>CC</sub> - 0.3 | v          |

| V <sub>IH</sub>  | Input High Voltage                                       | (Except XTAL1, RST)                                   | 0.2 V <sub>CC</sub> + 0.9 | V <sub>CC</sub> + 0.5     | v          |

| V <sub>IH1</sub> | Input High Voltage                                       | (XTAL1, RST)                                          | 0.7 V <sub>CC</sub>       | V <sub>CC</sub> + 0.5     | v          |

| VOL              | Output Low Voltage <sup>(1)</sup> (Ports 1,2,3)          | I <sub>OL</sub> = 1.6 mA                              |                           | 0.45                      | v          |

| V <sub>OL1</sub> | Output Low Voltage <sup>(1)</sup><br>(Port 0, ALE, PSEN) | i <sub>OL</sub> = 3.2 mA                              |                           | 0.45                      | v          |

| V <sub>OH</sub>  | Output High Voltage<br>(Ports 1,2,3, ALE, PSEN)          | $I_{OH} = -60 \ \mu A, V_{CC} = 5V \pm 10\%$          | 2.4                       |                           | v          |

|                  |                                                          | I <sub>OH</sub> = -25 μA                              | 0.75 V <sub>CC</sub>      |                           | v          |

|                  |                                                          | l <sub>OH</sub> = -10 μA                              | 0.9 V <sub>CC</sub>       |                           | v          |

| VoHI             | Output High Voltage<br>(Port 0 in External Bus Mode)     | I <sub>OH</sub> = -800 μA, V <sub>CC</sub> = 5V ± 10% | 2.4                       |                           | v          |

|                  |                                                          | I <sub>OH</sub> = -300 μA                             | 0.75 V <sub>CC</sub>      |                           | v          |

|                  |                                                          | I <sub>OH</sub> = -80 µA                              | 0.9 V <sub>CC</sub>       |                           | v          |

| l <sub>K_</sub>  | Logical 0 Input Current (Ports 1,2,3)                    | V <sub>IN</sub> = 0.45V                               |                           | -50                       | μ <b>A</b> |

| I <sub>TL</sub>  | Logical 1 to 0 Transition Current<br>(Ports 1,2,3)       | $V_{IN} = 2V, VCC = 5V \pm 10\%$                      |                           | -650                      | µA         |

| ί <sub>Li</sub>  | Input Leakage Current (Port 0, EA)                       | 0.45 < V <sub>IN</sub> < V <sub>CC</sub>              |                           | ±10                       | μ <b>A</b> |

| RRST             | Reset Pulldown Resistor                                  |                                                       | 50                        | 300                       | ΚΩ         |

| C <sub>IO</sub>  | Pin Capacitance                                          | Test Freq. = 1 MHz, T <sub>A</sub> = 25°C             |                           | 10                        | pF         |

| lcc              | Power Supply Current                                     | Active Mode, 12 MHz                                   |                           | 20                        | mA         |

|                  |                                                          | Idie Mode, 12 MHz                                     |                           | 5                         | mA         |

|                  | Power Down Mode <sup>(2)</sup>                           | V <sub>CC</sub> = 6V                                  |                           | 100                       | μ <b>A</b> |

|                  |                                                          | V <sub>cc</sub> = 3V                                  |                           | 40                        | μ <b>A</b> |

Notes: 1. Under steady state (non-transient) conditions, IOL must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Port 0: 28 m/

Port 0: 26 mA Ports 1, 2, 3: 15 mA

$\frac{1}{1} \frac{1}{2} \frac{1}$

Maximum total IOL for all output pins: 71 mA

If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Plns are not guaranteed to sink current greater than the listed test conditions.

2. Minimum V<sub>CC</sub> for Power Down is 2V.

# **AC Characteristics**

(Under Operating Conditions; Load Capacitance for Port 0, ALE/PROG, and PSEN = 100 pF; Load Capacitance for all other outputs = 80 pF)

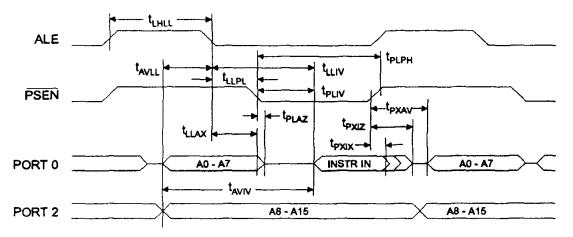

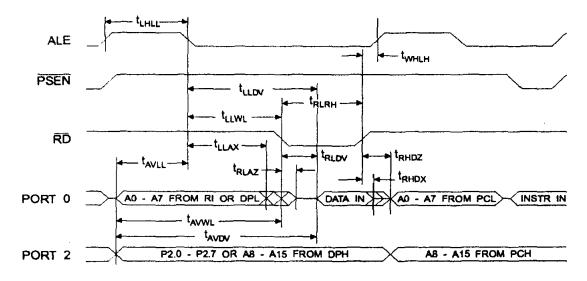

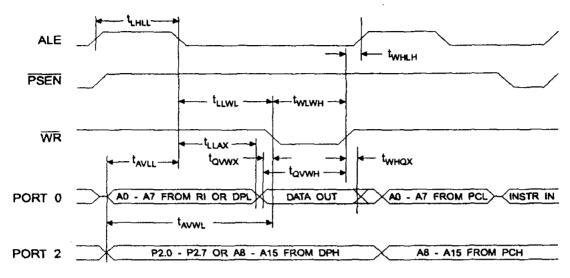

## **External Program and Data Memory Characteristics**

| Symbol            | Parameter                          | 12 MHz Oscillator |     | 16 to 24 MHz Oscillator |                         | Units |

|-------------------|------------------------------------|-------------------|-----|-------------------------|-------------------------|-------|

|                   |                                    | Min               | Max | Min                     | Max                     |       |

| 1ACLCL            | Oscillator Frequency               |                   | 1   | 0                       | 24                      | MHz   |

| чни               | ALE Pulse Width                    | 127               |     | 2tc1c1-40               |                         | ns    |

| tAVLL             | Address Valid to ALE Low           | 43                |     | t <sub>CLCL</sub> -13   |                         | ns    |

| t <sub>llax</sub> | Address Hold After ALE Low         | 48                |     | t <sub>CLCL</sub> -20   |                         | ាន    |

| tu.iv             | ALE Low to Valid Instruction In    |                   | 233 |                         | 4t <sub>CLCL</sub> -85  | ns    |

| 1 <sub>LLPL</sub> | ALE LOW to PSEN LOW                | 43                |     | t <sub>CLCL</sub> -13   |                         | ns    |

| 1PLPH             | PSEN Pulse Width                   | 205               |     | 3t <sub>CLCL</sub> -20  |                         | ns    |

| t <sub>PLIV</sub> | PSEN Low to Valid Instruction In   |                   | 145 |                         | 3t <sub>CLCL</sub> -45  | ns    |

| t <sub>PXIX</sub> | Input Instruction Hold After PSEN  | 0                 |     | 0                       |                         | ns    |

| texiz             | Input Instruction Float After PSEN |                   | 59  |                         | t <sub>CLCL</sub> -10   | ns    |

| t <sub>PXAV</sub> | PSEN to Address Valid              | 75                |     | tclcl-8                 |                         | ns    |

| 1 <sub>AVIV</sub> | Address to Valid Instruction In    |                   | 312 |                         | 5t <sub>CLCL</sub> -55  | ns    |

| 1 <sub>PLAZ</sub> | PSEN Low to Address Float          |                   | 10  |                         | 10                      | ns    |

| tRLRH             | RD Pulse Width                     | 400               |     | 6t <sub>CLCL</sub> -100 |                         | ns    |

| twinh             | WR Pulse Width                     | 400               |     | 6t <sub>CLCL</sub> -100 |                         | ns    |

| t <sub>RLDV</sub> | RD Low to Valid Data In            |                   | 252 |                         | 51 <sub>CLCL</sub> -90  | ns    |

| t <sub>RHDX</sub> | Data Hold After RD                 | 0                 |     | 0                       |                         | ns    |

| t <sub>RHDZ</sub> | Data Float After RD                |                   | 97  |                         | 21 <sub>CLCL</sub> -28  | ns    |

| turov             | ALE Low to Valid Data In           |                   | 517 |                         | 8t <sub>CLCL</sub> -150 | ns    |

| tAVDV             | Address to Valid Data In           |                   | 585 |                         | 9t <sub>CLCL</sub> -165 | ns    |

| tLLWL             | ALE Low to RD or WR Low            | 200               | 300 | 3t <sub>CLCL</sub> -50  | 3t <sub>CLCL</sub> +50  | ns    |

| tavwi.            | Address to RD or WR Low            | 203               |     | 4t <sub>CLCL</sub> -75  |                         | ns    |

| tavwx             | Data Valid to WR Transition        | 23                | }   | tolol-20                |                         | ns    |

| town:             | Data Valid to WR High              | 433               | [   | 7t <sub>CLCL</sub> -120 |                         | ns    |

| twhax             | Data Hold After WR                 | 33                |     | t <sub>CLCL</sub> -20   |                         | ns    |

| t <sub>RLAZ</sub> | RD Low to Address Float            |                   | 0   |                         | 0                       | ns    |

| twith             | RD or WR High to ALE High          | 43                | 123 | t <sub>CLCL</sub> -20   | tclcl+25                | ns    |

AT89C51

4-38

AT89C51

# **External Program Memory Read Cycle**

# **External Data Memory Read Cycle**

# External Data Memory Write Cycle

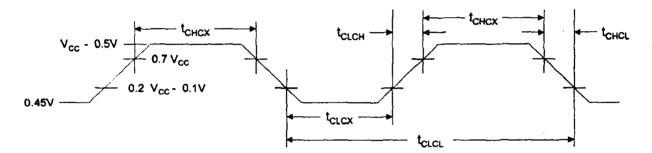

# **External Clock Drive Waveforms**

# **External Clock Drive**

| Symbol | Parameter            | Min  | Max | Units |

|--------|----------------------|------|-----|-------|

| 1ACLCL | Oscillator Frequency | 0    | 24  | MHz   |

| tala   | Clock Period         | 41.6 |     | ns    |

| тснсх  | High Time            | 15   |     | ns    |

| talax  | Low Time             | 15   |     | ns    |

| talch  | Rise Time            |      | 20  | ns    |

| t-CHCL | Fail Time            |      | 20  | ns    |

AT89C51

4-40

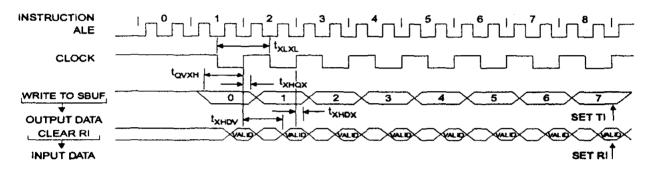

# Serial Port Timing: Shift Register Mode Test Conditions

| Symbol            | Parameter                                | 12 MHz Osc |     | Variable Oscillator      |                          | Units |

|-------------------|------------------------------------------|------------|-----|--------------------------|--------------------------|-------|

|                   |                                          | Min        | Max | Min                      | Max                      | ]     |

| t <sub>XLXL</sub> | Serial Port Clock Cycle Time             | 1.0        |     | 12t <sub>CLCL</sub>      |                          | μs    |

| tovxH             | Output Data Setup to Clock Rising Edge   | 700        |     | 10t <sub>CLCL</sub> -133 |                          | ns    |

| t <sub>xhox</sub> | Output Data Hold After Clock Rising Edge | 50         |     | 2t <sub>CLCL</sub> -117  |                          | ns    |

| txHDX             | Input Data Hold After Clock Rising Edge  | 0          |     | 0                        |                          | ns    |

|                   | Clock Rising Edge to Input Data Valid    |            | 700 |                          | 10t <sub>CLCL</sub> -133 | ns    |

$(V_{CC} = 5.0 \text{ V} \pm 20\%; \text{ Load Capacitance} = 80 \text{ pF})$

# Shift Register Mode Timing Waveforms

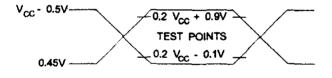

# AC Testing Input/Output Waveforms<sup>(1)</sup>

## Float Waveforms<sup>(1)</sup>

Note: 1. AC Inputs during testing are driven at V<sub>CC</sub> - 0.5V for a logic 1 and 0.45V for a logic 0. Timing measurements are made at V<sub>IH</sub> min. for a logic 1 and V<sub>IL</sub> max. for a logic 0.

Note: 1. For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs. A port pin begins to float when 100 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs.

# Ordering Information

| Speed<br>(MHz) | Power<br>Supply                         | Ordering Code | Package | Operation Range  |

|----------------|-----------------------------------------|---------------|---------|------------------|

| 12             | 5V ± 20%                                | AT89C51-12AC  | 44A     | Commercial       |

| )              |                                         | AT89C51-12JC  | 44J     | (0°C to 70°C)    |

|                |                                         | AT89C51-12PC  | 40P6    |                  |

|                | ,                                       | AT89C51-12QC  | 44Q     |                  |

|                |                                         | AT89C51-12AI  | 44A     | Industrial       |

|                |                                         | AT89C51-12JI  | 44J     | (-40°C to 85°C)  |

|                |                                         | AT89C51-12PI  | 40P6    |                  |

|                |                                         | AT89C51-12QI  | 44Q     |                  |

|                | Ì                                       | AT89C51-12AA  | 44A     | Automotive       |

|                |                                         | AT89C51-12JA  | 44J     | (-40°C to 105°C) |

|                | 1                                       | AT89C51-12PA  | 40P6    |                  |

|                |                                         | AT89C51-12QA  | 44Q     |                  |

| 16             | 5V ± 20%                                | AT89C51-16AC  | 44A     | Commercial       |

|                |                                         | AT89C51-16JC  | 44J     | (0°C to 70°C)    |

|                | ļ                                       | AT89C51-16PC  | 40P6    |                  |

|                |                                         | AT89C51-16QC  | 44Q     |                  |

|                | Ì                                       | AT89C51-16AI  | 44A     | industrial       |

|                |                                         | AT89C51-16JI  | 44J     | (-40°C to 85°C)  |

|                |                                         | AT89C51-16PI  | 40P6    |                  |

|                |                                         | AT89C51-16QI  | 44Q     |                  |

|                | t i i i i i i i i i i i i i i i i i i i | AT89C51-16AA  | 44A     | Automotive       |

|                |                                         | AT89C51-16JA  | 44J     | (-40°C to 105°C) |

|                |                                         | AT89C51-16PA  | 40P6    | •                |

|                |                                         | AT89C51-16QA  | 44Q     |                  |

| 20             | 5V ± 20%                                | AT89C51-20AC  | 44A     | Commercial       |

| 1              |                                         | AT89C51-20JC  | 44J     | (0°C to 70°C)    |

|                |                                         | AT89C51-20PC  | 40P6    |                  |

|                |                                         | AT89C51-20QC  | 44Q     |                  |

| ļ              | -                                       | AT89C51-20AI  | 44A     | Industrial       |

|                |                                         | AT89C51-20JI  | 44J     | (-40°C to 85°C)  |

|                | ľ                                       | AT89C51-20PI  | 40P6    | -                |

|                |                                         | AT89C51-20QI  | 44Q     |                  |

# **Ordering Information**

| Speed<br>(MHz) | Power<br>Supply | Ordering Code | Package | Operation Range |

|----------------|-----------------|---------------|---------|-----------------|

| 24             | 5V ± 20%        | AT89C51-24AC  | 44A     | Commercial      |

|                |                 | AT89C51-24JC  | 44J     | (0°C to 70°C)   |

|                |                 | AT89C51-24PC  | 44P6    |                 |

|                |                 | AT89C51-24QC  | 44Q     |                 |

|                |                 | AT89C51-24AI  | 44A     | Industriai      |

|                |                 | AT89C51-24JI  | 44J     | (-40°C to 85°C) |

|                |                 | AT89C51-24PI  | 44P6    |                 |

|                |                 | AT89C51-24QI  | 44Q     |                 |

PERPUSTAXAAN Universitas Katolik View a manuala SUKADAA

.

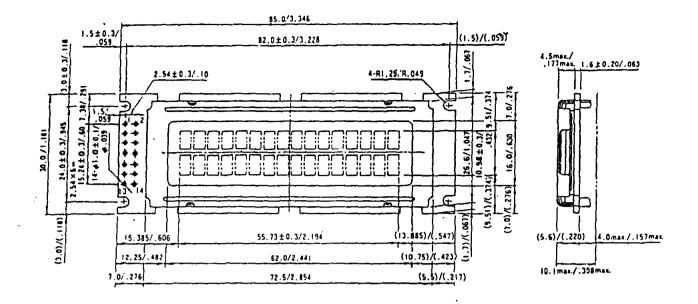

|      | Package Type                                             |     |

|------|----------------------------------------------------------|-----|

| 44A  | 44 Lead, Thin Plastic Gull Wing Quad Flatpack (TQFP)     |     |

| 44J  | 44 Lead, Plastic J-Leaded Chip Carrier (PLCC)            |     |

| 40P6 | 40 Lead, 0.600" Wide, Plastic Dual Inline Package (PDIP) | D . |

| 44Q  | 44 Lead, Plastic Gull Wing Quad Flatpack (PQFP)          | •   |

3.53/.139

0.07. .003

0.50/.020

0.55/.022

0.01/.003

4.89/.193

110./2.

6.09/.240

Unit : mm/inch General tolerance : ±0.5 mm

|             | No. | Symbol | Level |                         | Function             |

|-------------|-----|--------|-------|-------------------------|----------------------|

| 0.75/.030   | 1   | Vss    | -     |                         | OV (GND)             |

|             | 2   | Vcc    | •     | Power                   | 5V ±10%              |

|             | 3   | Vee    |       | Supply                  | for LCD Drive        |

|             | 4   | RS     | H/L   | H: Data I<br>L: Instruc | nput<br>tion Input   |

|             | 5   | R/W    | H/L   | H:READ                  | L:WRITE              |

|             | 6   | E      | Н, Ъ  | Enable Si               | gnal                 |

|             | 7   | DB0    | H/L   | Ţ                       |                      |

|             | 8   | DBI    | H/L   | ] [                     |                      |

| ··          | 9   | DB2    | H/L   |                         |                      |

|             | 10_ | _DB3_  | HL    | 1                       |                      |

|             | 11  | DB4    | H/L   | Data Bus                |                      |

|             | 12  | DB5    | HIL   | [                       |                      |

| ĺ           | 13  | DB6    | IIL   |                         |                      |

|             | 14  | DB7    | H/L   |                         |                      |

| ons diagran | 15  | V+ BL  | -     | Back<br>Light           | 4 - 4.2V<br>50-200mA |

| - (         | 16  | V- BL  |       | Supply                  | 0V (GND)             |

Figure 1 Dimensions d

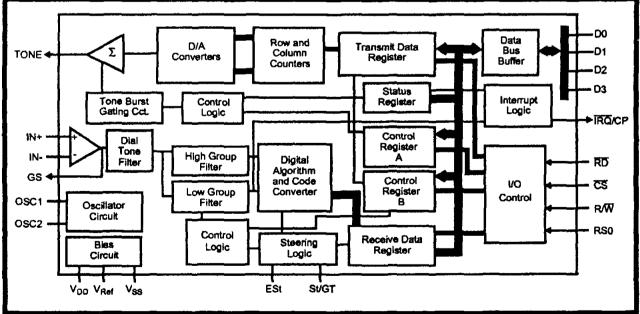

### INTRODUCTION

Selko Instruments intelligent dot matrix liquid crystal display modules have on-board controller and LSI drivers, which display alpha numerics, Japanese KATA KANA characters and a wide variety of other symbols in either 5 x 7 dot matrix.

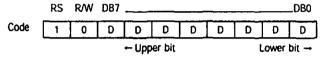

The internal operation in the KS0066 controller chip is determined by signals sent from the MPU. The signals

include: 1) Register select RS input consisting of instruction register (IR) when RS = 0 and data register (DR) when RS = 1; 2) Read/write (R/W); 3) Data bus (DB7~ DB0); and 4) Enable strobe (E) depending on the MPU or through an external parallel I/O port. Details on instructions data entry, execution times, etc. are explained in the following sections.

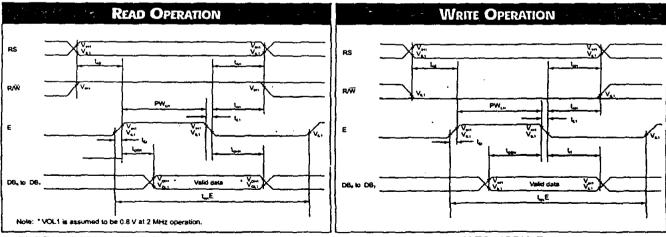

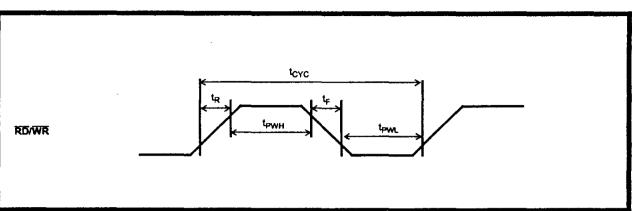

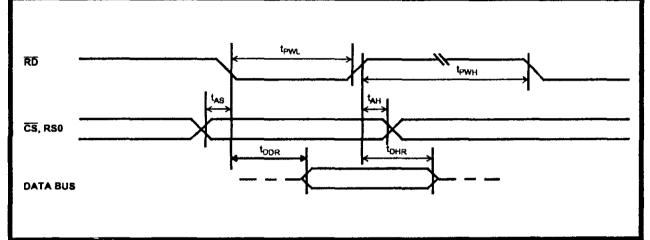

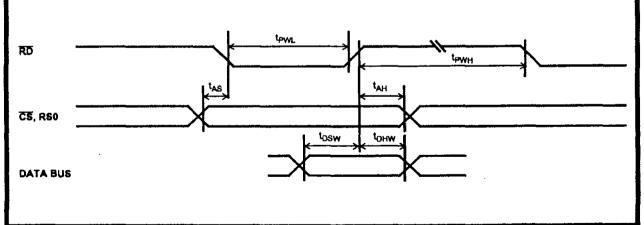

## **READ AND WRITE TIMING DIAGRAMS AND TABLES**

The following timing characteristics are applicable for all of Seiko's LCD dot matrix character modules.

| READ TIMING CHARACTERISTICS<br>V==5.0V±5%, V==0°C to 50°C |                    |      |      |      |  |  |  |  |  |  |

|-----------------------------------------------------------|--------------------|------|------|------|--|--|--|--|--|--|

| ltem                                                      | Symbol             | Stan | dard | Unit |  |  |  |  |  |  |

|                                                           |                    | Min. | Max. |      |  |  |  |  |  |  |

| Enable cycle time                                         | t <sub>cvc</sub> E | 500  |      | ns   |  |  |  |  |  |  |

| Enable pulse width High Level                             | PW <sub>EH</sub>   | 230  |      | ns   |  |  |  |  |  |  |

| Enable rise and fall time                                 | ten, ter           |      | 20   | ns   |  |  |  |  |  |  |

| Address setup time RS,R/W-E                               | t <sub>AS</sub>    | 40   |      | ns   |  |  |  |  |  |  |

| Address hold time                                         | t <sub>ari</sub>   | 10   |      | ns   |  |  |  |  |  |  |

| Data delay time                                           | LOOR               |      | 160  | ns   |  |  |  |  |  |  |

| Data hold time                                            | t <sub>ri</sub>    | 5    | —    | ns   |  |  |  |  |  |  |

| WRITE TIMING<br>V∞=5.0V±5%, V∞ |                    |      |      | , +<br>., |

|--------------------------------|--------------------|------|------|-----------|

| ltem                           | Symbol             | Stan | dard | Unit      |

|                                |                    | Min. | Max. |           |

| Enable cycle time              | t <sub>cyc</sub> E | 500  |      | ns        |

| Enable pulse width High Level  | PWEH               | 230  |      | ns        |

| Enable rise and fall time      | LER. LEF           |      | 20   | ns        |

| Address setup time RS,RW-E     | t <sub>as</sub>    | 40   |      | ាន        |

| Address hold time              | t <sub>AH</sub>    | 10   |      | ns        |

| Data setup time                | Losw               | 80   | '    | ns        |

| Data hold time                 | t <sub>ii</sub>    | 10   |      | ns        |

DATA READ FROM MODULE TO MPU

DATA WRITE FROM MPU TO MODULE

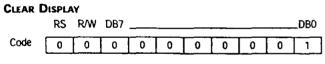

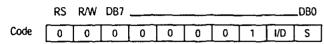

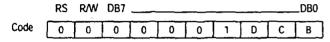

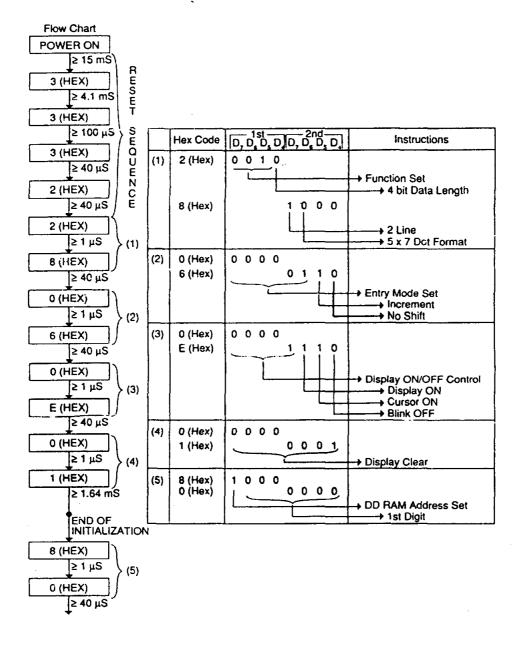

# INTRODUCTION CODES

| Instruction                               | -    | iet . : |     | Daa        |      | ruction (       |     | - 804 |     |     | Description                                                                                                                         | Execution Time<br>(when f <sub>cp</sub> or f <sub>ose</sub> |

|-------------------------------------------|------|---------|-----|------------|------|-----------------|-----|-------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 4 - 1 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 | - RS | RW      | D87 | D86        | DBS  | DB4             | DB3 | DB2   | DB1 | DB0 |                                                                                                                                     | _(s 250 kHz)                                                |

| Clear Display                             | 0    | 0       | 0   | 0          | o    | 0               | 0   | 0     | 0   | 1   | Clears all display memory and<br>returns the cursor to the home<br>position (Address 0).                                            | 82 µs ~ 1.64ms                                              |

| Return Home                               | 0    | 0       | 0   | 0          | 0    | 0               | 0   | 0     | 1   | •   | Returns the cursor to the<br>home position (Address 0)<br>shifted to the original position.<br>DD RAM contents remain<br>unchanged. | 40 µs - 1.6ms                                               |

| Entry<br>Mode Set                         | 0    | 0       | 0   | 0          | 0    | 0               | 0   | 1     | I/D | s   | Sets the cursor move direction<br>and specifies to or not to shift<br>the display. These operations<br>write and read.              | 40 µs - 1.64ms                                              |

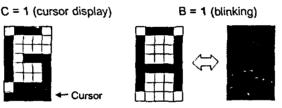

| Display<br>ON/OFF<br>Control              | o    | 0       | 0   | 0          | 0    | o               | 1   | D     | с   | В   | (D) is display ON/OFF control;<br>memory remains unchanged<br>in OFF condition. (C) cursor<br>ON/OFF (B) blinking cursor.           | 40 µs                                                       |

| Cursor or<br>Display Shift                | 0    | 0       | 0   | 0          | 0    | 1               | s/c | R/L   | •   | •   | Moves the cursor and shifts<br>the display without changing<br>DD RAM contents.                                                     | . <b>40</b> μs                                              |

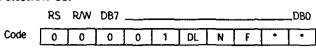

| Function Set                              | 0    | 0       | ٥   | 0          | 1    | DL              | N   | F     | •   | •   | Sets interface data length<br>(DL), number of display lines<br>(N), and character font (F).                                         | 40 µS                                                       |

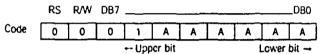

| Set CG RAM<br>Address                     | 0    | o       | 0   | 1          |      |                 | Acc |       | _   |     | Sets the CG RAM address.<br>CG RAM data is sent and<br>received after this setting.                                                 | 40 µs                                                       |

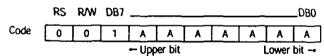

| Set DD RAM<br>Address                     | 0    | 0       | 1   | <b>_</b>   |      | A <sub>00</sub> | _   |       |     |     | Sets the DD RAM address.<br>DD RAM data is sent and<br>received after this setting.                                                 | 40 µS                                                       |

| Read<br>Busy Flag<br>& Address            | 0    | 1       | ßF  |            | AC   |                 |     |       |     |     | Reads Busy Flag (BF)<br>indicating internal operation is<br>being performed and reads<br>address counter contents.                  | 1 µS                                                        |

| Write Data<br>to CG or<br>to DD RAM       | 1    | o       |     | Write Data |      |                 |     |       |     |     | Writes data into DD RAM or<br>CG RAM.                                                                                               | 40 µs                                                       |

| Read Data<br>from CG or<br>DD RAM         | 1    | 1       |     |            | Read | l Data          |     |       |     |     | Reads data from DD RAM or CG RAM.                                                                                                   | 40 µS                                                       |

| DD RAM: | Display data RAM                 | VD = 1: | Increment        | C = 1:             | Cursor ON                      | R/L = 1: | Right shift      |

|---------|----------------------------------|---------|------------------|--------------------|--------------------------------|----------|------------------|

| CG RAM: | Character generator RAM          | VD = 0: | Decrement        | C = 0:             | Cursor Off                     | R/L = 0: | Left shift       |

| ACG:    | CG RAM address                   | S = 1:  | Display shift    | 8=1:               | Blink ON<br>Blink OFF          | DL = 1;  | 8 bits           |

| ADD     | DD RAM address corresponds to    | S = 0:  | No display shift | B = 0:<br>S/C = 1; | Display shift                  | DL = 0;  | 4 bits           |

|         | cursor address                   | D = 1:  | Display ON       | S/C = 0:           | Cursor movement                | N = 1:   | 2 lines (L.1671) |

| Ac:     | Address counter used for both DD | D = 0:  | Display OFF      | BF = 1:            | Internal operation in progress | R = 1.   | 2 miles (L 1071) |