## LAMPIRAN A

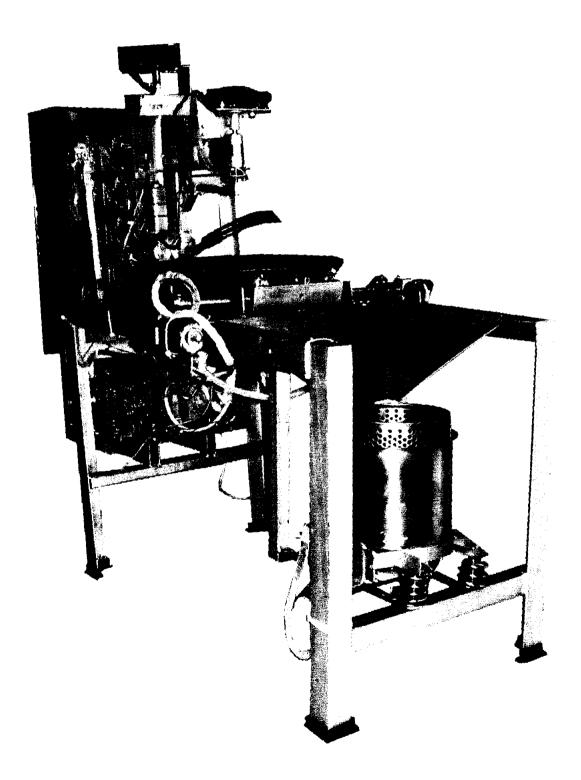

## Gambar Alat

#### LAMPIRAN C

#### LISTING MIKROKONTROLLER

```

#include<stdio.h>

#include<regx51.h>

sbit DQ = P0_4;

sfr ldata = 0x90;

sbit rs = P3 0;

sbit en = P3 1;

unsigned int suhu;

char a;

int b,c,d,e,f;

void delay(int useconds)

£

int s:

for (s=0; s<useconds;s++);</pre>

unsigned char ow reset(void)

ſ

unsigned char presence;

DQ = 0; //pull DQ line low

delay(29); // leave it low for 480is

DQ = 1; // allow line to return high

delay(3); // wait for presence

presence = DQ; // get presence signal

delay(25); // wait for end of timeslot

return(presence); // presence signal returned

} // 0=presence, 1 = no part

unsigned char read bit(void)

ł

unsigned char i;

DQ = 0; // pull DQ low to start timeslot

DQ = 1; // then return high

for (i=0; i<3; i++); // delay 151s from start of timeslot return(DQ); // return value of DQ line

}

void write_bit(char bitval)

DQ = 0; // pull DQ low to start timeslot

if(bitval==1) DQ =1; // return DQ high if write 1

delay(5); // hold value for remainder of timeslot

DQ = 1;

}

unsigned char read_byte(void)

{

unsigned char i;

unsigned char value = 0;

for (i=0;i<8;i++)

if(read_bit()) value = 0x01<<i; // reads byte in, one bit at a time and then

// shifts it left

delay(6); // wait for rest of timeslot

return(value);

ł

void write byte(char val)

ſ

unsigned char i;

unsigned char temp;

for (i=0; i<8; i++) // writes byte, one bit at a time

temp = val>>i; // shifts val right 'i' spaces

temp s = 0x01; // copy that bit to temp

write bit(temp); // write bit in temp into

}

```

```

delay(5);

}

void MSDelay(unsigned int itime)

{

unsigned int i, j;

for(i=0;i<itime;i++)</pre>

for(j=0;j<1275;j++);

}

void lcddata(unsigned char value)

{ldata = value;

rs = 1:

en = 1;

MSDelay(20);

en = 0;

return;

}

void tampilkan_ke_lcd(char *tulisan)

{

char hitung_tulisan;

while (hitung tulisan=*tulisan++)

lcddata(hitung_tulisan);

};

}

unsigned char Read_Current (void)

int lsb, msb, temp, nilai;

float Current; //This value may be declared globally

if(ow_reset()==0) //If a presence is detected, continue to read

write_byte(0xCC); // Skip Net Address Command

write_byte(0x69); // Read Registers Command

write_byte(0x0E); //Current Register Address

msb = read_byte(); // Read msb

lsb = read byte() & 0xF8; // Read lsb and mask off lower 3 bits

suhu = 256 \star msb + 1sb;

suhu = 65535 - suhu;

suhu = suhu/4;

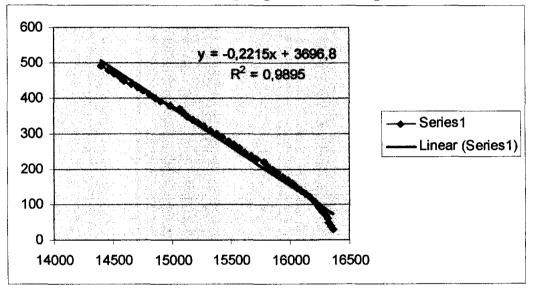

nilai = suhu*(-0.2215)+3698.8;

if (nilai >100 & nilai < 200)

{nilai=nilai-20;}

if (nilai < 100)

{nilai=nilai-40;}

lcddata(nilai/100 %10 + 0x30);

lcddata(nilai/10

%10 + 0x30);

%10 + 0x30);

lcddata(nilai

lcddata(0xDF);

lcddata('C');

return(0); //Return 0 if no error

}

return(1); //Return 1 if no presence detected

}

void motor putar()

{P3_7 = 1;}

void motor_aduk()

\{P2, 4 = 1;

P2_{5} = 1;

void motor wajan()

\{P2_2 = 1; // on

P2_3 = 1; //balik

void pemanas1()

\{P2 \ 6 = 1;

```

```

P2_7 = 1;

}

void pemanas2()

\{P2_6 = 0; P2_7 = 0; P2_7 = 0; \}

)

void posisi()//akuuuu

{satu:

if (PO_5 == 0)

P2_4 = 0;

else

goto satu;

dua:

MSDelay(1000);

if (P0_6 == 0)

P2_5 = 0;

else

goto dua;

1

void lcdcmd(unsigned char value)

ſ

ldata = value;

rs = 0;

en = 1;

MSDelay(20);

en = 0;

return;

ł

void wajan naik()

(1cdcmd(0x01);

tampilkan ke lcd("penirisan");

MSDelay(1000);

P2 \ 1 = 1;

//////motor atas

MSDelay(100);

P2 \ 1 = 0;

MSDelay(200);

P2_1 = 1;

MSDelay(1000);

P2 1 = 0;

MSDelay(1000);

////motor wajan

P2 \ 3 = 1;

while(P0_3 != 0);

P2_2 = 1;

MSDelay(50);

P2 = 0x00;

}

void wajan_turun()

\{P2 = 0x0C;

MSDelay(100);

P2 = 0x00;

MSDelay(2000);/////motor wajan

P2_1 = 1;

P2_0 = 1;

MSDelay(100);

P2 = 0x00;

MSDelay(100);

P2 = 0x03;

MSDelay(200);//motor atas

P2 = 0x00;

}

void init_lcd()

{lcdcmd(0x038);

MSDelay(20);

lcdcmd(0x0C);

MSDelay(20);

lcdcmd(0x06);

MSDelay(20);

lcdcmd(0x01);

```

```

MSDelay(20);

}

void mulai()

{

pemanas1();

a = 0;

while(P0_3 != 0)

\{P3_2 = \overline{0};

if (P0_3 !=0)

MSDelay(500);

P3_2 = 1;

if (P0_3 !=0)

{MSDelay(500);}

a++;

if (a>10)

break;

}

if (a>=10)

{P3_2 = 0;

while (P0_3 != 0)

Ł

if (P0_3 !=0)

MSDelay(1000);

if (suhu < 15597)

pemanas2();

else

pemanas1();

}

}

lcdcmd(0x01);

pemanas1();

P3 2 = 1;

lcdcmd(0x01);

tampilkan_ke_lcd("tunggu suhu");

1 cdcmd(0xC4);

read_current();

while (suhu > 14687)

(lcdcmd(0xC4);

read current();

MSDelay(1000);

}

3

void daging()

ſ

lcdcmd(0x01);

tampilkan_ke_lcd("masukkan");

lcdcmd(0xC0);

tampilkan_ke_lcd("daging + bumbu");

a = 0;

while(P0_3 != 0)

\{P3_2 = 0; \\ if (P0_3 !=0)\}

MSDelay(500);

P3 2 = 1;

if (P0_3 !=0)

MSDelay(1000);

a++;

if (a>10)

break;

}

if (a>=10)

{P3_2 = 0;

while (P0_3 != 0);

1

P3 2 = 1;

lcdcmd(0x01);

ł

void daging bumbu()

ł

```

```

lcdcmd(0x01);

tampilkan_ke_lcd("masukkan");

lcdcmd(0xC0);

tampilkan ke lcd("daging berbumbu");

MSDelay(1000);

a = 0;

while (PO 3 != 0)

\{P3 \ 2 = \overline{0};

if (P0_3 !=0)

MSDelay(500);

P3_2 = 1;

if (P0_3 !=0)

MSDelay(1000);

a++;

if (a>10)

break;

if (a>=10)

\{P3_2 = 0;

while (P0_3 != 0);

ł

P3 2 = 1;

lcdcmd(0x01);

ł

void waktu()

{

c = 0;

tampilkan_ke_lcd("sisa ");

if(b!=f)

motor_aduk();

while (b != 0)

{if (b == d)

posisi();

if (b == e)

motor_aduk();

lcdcmd(0x85);

%10 + 0x30);

lcddata(b/10

lcddata(b

%10 + 0x30);

tampilkan_ke_lcd(" menit");

c = 0;

while (c <= 173)

(lcdcmd(0xc4);

read_current();

MSDelay(10);

c++;

}

b--;

}

}

void waktu_kering()

{c = 0;}

while (b != 0)

{c = 0;}

while (c <= 233)

{MSDelay(100);

c++;

}

b--;

F

}

void main(void)

\{P3 = 0x04;

P1 = 0x00;

P2 = 0x00;

P0 = 0xff;

init_lcd();

lcdcmd(0x01);

lcdcmd(0x84);

tampilkan_ke_lcd("wibisono");

lcdcmd(0xc3);

```

```

tampilkan_ke_lcd("5103003007");

while (P0_{3} = 0);

lcdcmd(0x01);

tampilkan ke lcd("tombol 1 = 100g");

lcdcmd(0xc0);

tampilkan_ke_lcd("tombol 2 = 250g");

while(1)

(if (PO 0 == 0))

\{1cdcmd(\overline{0}x01);

tampilkan ke lcd("masukkan minyak");

lcdcmd(0xc0);

tampilkan ke lcd("2 sendok makan");

mulai();

daging();

b=10;

d=5;

e=25;

f=25;

waktu();

pemanas2();

wajan naik();

MSDelay(500);

wajan_turun();

motor_putar();

b=3;

waktu_kering();

P3 7 = 0;//goreng

pemanas1();

lcdcmd(0x01);

tampilkan ke lcd("masukkan minyak");

lcdcmd(0xc0);

tampilkan_ke_lcd("200 ml");

mulai();

daging_bumbu();

b=20;

d=5;

e=15;

f=20;

waktu();

pemanas2();

wajan naik();

MSDelay(500);

wajan_turun();

motor putar();

b=3;

waktu_kering();

P3 7 = 0;

lcdcmd(0x01);

tampilkan_ke_lcd("selesai!!!!!");

while (P0_3 != 0)

\{P3_2 = 0;

if (P0 3 !=0)

MSDelay(500);

P3 2 = 1;

if (P0_3 !=0)

MSDelay(1000);

lcdcmd(0x01);

lcdcmd(0x80);

tampilkan ke lcd("tombol 1 = 100g");

lcdcmd(0xc0);

tampilkan ke lcd("tombol 2 = 250g");

}

else

if (P0_1 == 0)

{lcdcmd(0x01);

tampilkan ke lcd("masukkan minyak");

lcdcmd(0xc0);

tampilkan_ke_lcd("2 sendok makan");

mulai();

```

```

daging();

b=10;

d=5;

e=25;

f=15;

waktu();

pemanas2();

wajan_naik();

MSDelay(500);

wajan_turun();

motor_putar();

b=3;

waktu_kering();

P3_7 = 0;//goreng

pemanas1();

lcdcmd(0x01);

tampilkan_ke_lcd("masukkan minyak");

lcdcmd(0xc0);

tampilkan_ke_lcd("300 ml");

mulai();

daging_bumbu();

b=30;

d=10;

e=20;

f=30;

waktu();

pemanas2();

wajan_naik();

MSDelay(500);

wajan_turun();

motor_putar();

b=3;

waktu_kering();

P3_7 = 0;

lcdcmd(0x01);

tampilkan_ke_lcd("selesai!!!!!");

while(P0_3 != 0)

{P3_2 = 0;

if (P0_3 !=0)

MSDelay(500);

P3_2 = 1;

if (P0_3 !=0)

MSDelay(1000);

}

lcdcmd(0x01);

lcdcmd(0x80);

tampilkan_ke_lcd("tombol 1 = 100g");

lcdcmd(0xc0);

tampilkan ke lcd("tombol 2 = 250g");

}

//motor_aduk();

ł

}

```

## LAMPIRAN D

## DATA PENGAMBILAN SAMPEL

|                     | Tabel Sai                    | npel                   |          |

|---------------------|------------------------------|------------------------|----------|

| DS2760              | Multimeter UNI-T Type UT720B | Hasil dari persamaan Y | Selisih  |

| 16365               | 30                           | 71,9525                | 41,9525  |

| 16347               | 40                           | 75,9395                | 35,9395  |

| 16331               | 50                           | 79,4835                | 29,4835  |

| 16313               | 60                           | 83,4705                | 23,4705  |

| 16295               | 70                           | 87,4575                | 17,4575  |

| 16273               | 80                           | 92,3305                | 12,3305  |

| 16249               | 90                           | 97,6465                | 7,6465   |

| 16225               | 100                          | 102,9625               | 2,9625   |

| <b>16</b> 195       | 110                          | 109,6075               | -0,3925  |

| 16159               | 120                          | 117,5815               | -2,4185  |

| 16129               | 130                          | 124,2265               | -5,7735  |

| 16091               | 140                          | 132,6435               | -7,3565  |

| 16051               | 150                          | 141,5035               | -8,4965  |

| 16013               | 160                          | 149,9205               | -10,0795 |

| 15979               | 170                          | 157,4515               | -12,5485 |

| 15933               | 180                          | 167,6405               | -12,3595 |

| 15891               | 190                          | 176,9435               | -13,0565 |

| 15 <mark>849</mark> | 200                          | 186,2465               | -13,7535 |

| 15803               | 210                          | 196,4355               | -13,5645 |

| 15775               | 220                          | 202,6375               | -17,3625 |

| 15715               | 230                          | 215,9275               | -14,0725 |

| 15667               | 240                          | 226,5595               | -13,4405 |

| 15613               | 250                          | 238,5205               | -11,4795 |

| 15567               | 260                          | 248,7095               | -11,2905 |

| 15523               | 270                          | 258,4555               | -11,5445 |

| 15475               | 280                          | 269,0875               | -10,9125 |

| 15423               | 290                          | 280,6055               | -9,3945  |

| 15377               | 300                          | 290,7945               | -9,2055  |

| 15327               | 310                          | 301,8695               | -8,1305  |

| 15265               | 320                          | 315,6025               | -4,3975  |

| 15225               | 330                          | 324,4625               | -5,5375  |

| 15181               | 340                          | 334,2085               | -5,7915  |

| 15129               | 350                          | 345,7265               | -4,2735  |

| 15091               | 360                          | 354,1435               | -5,8565  |

| 15065               | 370                          | 359,9025               | -10,0975 |

| 14981               | 380                          | 378,5085               | -1,4915  |

| 14901               | 390                          | 396,2285               | 6,2285   |

| 14861               | 400                          | 405,0885               | 5,0885   |

| 14811               | 410                          | 416,1635               | 6,1635   |

| 14761               | 420                          | 427,2385               | 7,2385   |

**Tabel Sampel**

| DS2760 | Multimeter UNI-T Type UT720B | Hasil dari persamaan Y | Selisih |  |  |  |  |

|--------|------------------------------|------------------------|---------|--|--|--|--|

| 14711  | 430                          | 438,3135               | 8,3135  |  |  |  |  |

| 14657  | 440                          | 450,2745               | 10,2745 |  |  |  |  |

| 14597  | 450                          | 463,5645               | 13,5645 |  |  |  |  |

| 14561  | 460                          | 471,5385               | 11,5385 |  |  |  |  |

| 14509  | 470                          | 483,0565               | 13,0565 |  |  |  |  |

| 14461  | 480                          | 493,6885               | 13,6885 |  |  |  |  |

| 14403  | 490                          | 506,5355               | 16,5355 |  |  |  |  |

#### Tabel Sampel (lanjutan)

## Grafik dari pengambilan sampel

## BIODATA

Nama: WibisonoNRP: 5103003007Tempat/ Tgl. Lahir: Surabaya / 1 April 1982Agama: KatholikAlamat Rumah: Jl. Tarmidi 52

Samarinda – Kalimantan Timur

#### **Riwayat Pendidikan :**

- Tahun 1988, Lulus TK Kristus Radja Surabaya.

- Tahun 1996, Lulus SD Swasta Megawati Surabaya.

- Tahun 1999, Lulus SLTP Katholik Santa Agnes Surabaya.

- Tahun 2003, Lulus SMK Katholik St. Louis Surabaya.

- Tahun 2003 hingga buku ini ditulis, tercatat sebagai mahasiswa di Jurusan Teknik Elektro, Fakultas Teknik, Universitas Katolik Widya Mandala, Surabaya.

#

## **DS2760** High-Precision Li+ Battery Monitor

#### .maxim-ic.com

#### TURES

- + safety circuit

- Overvoltage protection

- Overcurrent/short circuit protection

- Undervoltage protection

- ro Volt Battery Recovery Charge vailable in two configurations:

- Internal  $25m\Omega$  sense resistor

- External user-selectable sense resistor urrent measurement

- 12-bit bidirectional measurement

- Internal sense resistor configuration:

- 0.625mA LSB and  $\pm 1.9$ A dynamic range

- External sense resistor configuration:

- 15.625µV LSB and ±64mV dynamic range urrent accumulation

- Internal sense resistor: 0.25mAhr LSB

- External sense resistor: 6.25µVhr LSB

- oltage measurement with 4.88mV resolution

- emperature measurement using integrated msor with 0.125°C resolution

- ystem power management and control feature ipport

- 2 bytes of lockable EEPROM

- 6 bytes of general purpose SRAM allas 1-Wire<sup>®</sup> interface with unique 64-bit IS1 - Current sense input

- evice address

- ow power consumption:

- Active current: 90µA max

- Sleep current: 2µA max

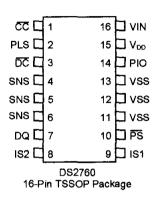

## PIN ASSIGNMENT

Flip-Chip Packaging Top View

#### PIN DESCRIPTION

- $\overline{\mathrm{CC}}$ - Charge control output

- $\overline{DC}$  Discharge control output

- DO Data input/output

- PIO Programmable I/O pin

- PLS Battery pack positive terminal input

- PS - Power switch sense input

- VIN Voltage sense input

- $V_{DD}$  Power supply input (2.5V to 5.5V)

- VSS Device ground

- SNS Sense resistor connection

- IS2 Current sense input

- SNS Probe Do not connect

- VSS Probe Do not connect

| ERING INFO   | RMATION  |                                                                 |

|--------------|----------|-----------------------------------------------------------------|

| Part         | Marking  | Description                                                     |

| 50AE+        | DS2760A  | TSSOP, External Sense Resistor, 4.275V Vov, Lead-Free           |

| 50BE+        | DS2760B  | TSSOP, External Sense Resistor, 4.35V Vov, Lead-Free            |

| 60AE+T&R     | DS2760A  | DS2760AE+ on Tape & Reel, Lead-Free                             |

| 60 BE+T&R    | DS2760B  | DS2760BE+ on Tape & Reel, Lead-Free                             |

| 60AE+025     | 2760A25  | TSSOP, 25mΩ Sense Resistor, 4.275V Vov, Lead-Free               |

| 60BE+025     | 2760B25  | TSSOP, 25mΩ Sense Resistor, 4.35V Vov, Lead-Free                |

| 60AE+025/T&R | 2760A25  | DS2760AE+025 in Tape & Reel, Lead-Free                          |

| 60BE+025/T&R | 2760B25  | DS2760BE+025 in Tape & Reel, Lead-Free                          |

| 60AX         | DS2760A  | Flipchip, External Sense Resistor, Tape & Reel, 4.275V Vov      |

| 60BX         | DS2760B  | Flipchip, External Sense Resistor, Tape & Reel, 4.35V Vov       |

| 60AX-025     | DS2760AR | Flipchip, $25m\Omega$ Sense Resistor, Tape & Reel, $4.275V$ Vov |

| 60BX-025     | DS2760BR | Flipchip, $25m\Omega$ Sense Resistor, Tape & Reel, 4.35V Vov    |

| 60AE         | DS2760A  | TSSOP, External Sense Resistor, 4.275V Vov                      |

| 60BE         | DS2760B  | TSSOP, External Sense Resistor, 4.35V Vov                       |

| 60AE/T&R     | DS2760A  | DS2760AE on Tape & Reel                                         |

| 60 BE/T&R    | DS2760B  | DS2760BE on Tape & Reel                                         |

| 60AE-025     | 2760A25  | TSSOP, $25m\Omega$ Sense Resistor, $4.275V$ Vov                 |

| 60BE-025     | 2760B25  | TSSOP, 25mΩ Sense Resistor, 4.35V Vov                           |

| 60AE-025/T&R | 2760A25  | DS2760AE-025 in Tape & Reel                                     |

| 60BE-025/T&R | 2760B25  | DS2760BE-025 in Tape & Reel                                     |

#### CRIPTION

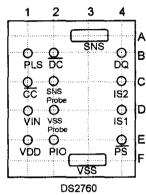

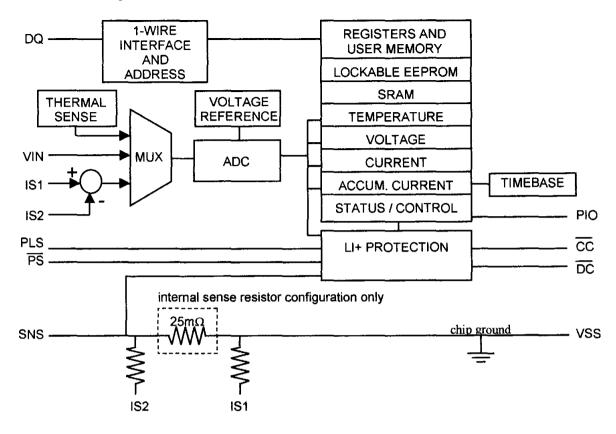

DS2760 High-Precision Li+ Battery Monitor is a data acquisition, information storage, and safety ction device tailored for cost-sensitive battery pack applications. This low-power device integrates se temperature, voltage, and current measurement, nonvolatile data storage, and Li+ protection into mall footprint of either a TSSOP package or flip chip. The DS2760 is a key component in cations including remaining capacity estimation, safety monitoring, and battery-specific data storage.

ts 1-Wire interface, the DS2760 gives the host system read/write access to status and control ters, instrumentation registers, and general purpose data storage. Each device has a unique factory-ammed 64-bit net address which allows it to be individually addressed by the host system, briting multi-battery operation.

DS2760 is capable of performing temperature, voltage and current measurement to a resolution tient to support process monitoring applications such as battery charge control, remaining capacity ation, and safety monitoring. Temperature is measured using an on-chip sensor, eliminating the need separate thermistor. Bidirectional current measurement and accumulation are accomplished using an internal  $25m\Omega$  sense resistor or an external device. The DS2760 also features a programmable in that allows the host system to sense and control other electronics in the pack, including switches, tion motors, speakers and LEDs.

e types of memory are provided on the DS2760 for battery information storage: EEPROM, lockable ROM and SRAM. EEPROM memory saves important battery data in true nonvolatile memory that affected by severe battery depletion, accidental shorts or ESD events. Lockable EEPROM becomes I when locked to provide additional security for unchanging battery data. SRAM provides bensive storage for temporary data.

## **CK DIAGRAM** Figure 1

J

## AILED PIN DESCRIPTION Table 1

| BOL         | TSSOP*   | FLIP  | DESCRIPTION                                                                                                                                                                                                                                                                                                                     |

|-------------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |          | CHIP* |                                                                                                                                                                                                                                                                                                                                 |

| ĪC          | 1        | C1    | Charge Protection Control Output. Controls an external p-channel high-side charge protection FET.                                                                                                                                                                                                                               |

| ж           | 3        | B2    | <b>Discharge Protection Control Output.</b> Controls an external p-channel high-side discharge protection FET.                                                                                                                                                                                                                  |

| Q           | 7        | B4    | <b>Data Input/Out.</b> 1-Wire data line. Open-drain output driver. Connect this pin to the DATA terminal of the battery pack. Pin has an internal $1\mu$ A pull-down for sensing disconnection.                                                                                                                                 |

| Ю           | 14       | E2    | <b>Programmable I/O Pin.</b> Used to control and monitor user-defined external circuitry. Open drain to VSS.                                                                                                                                                                                                                    |

| LS          | 2        | Bl    | <b>Battery Pack Positive Terminal Input.</b> The device monitors the state of the battery pack's positive terminal through this pin in order to detect events such as the attachment of a charger or the removal of a short circuit. Additionally, a charge path to recover a deeply depleted cell is provided from PLS to VDD. |

| PS          | 10       | E4    | <b>Power Switch Sense Input.</b> The device wakes up from Sleep Mode when it senses the closure of a switch to VSS on this pin. Pin has an internal $1\mu$ A pull-up to V <sub>DD</sub> .                                                                                                                                       |

| IN          | 16       | D1    | Voltage Sense Input. The voltage of the Li+ cell is monitored via this input pin. This pin has a weak pullup to $V_{DD}$ .                                                                                                                                                                                                      |

| DD          | 15       | E1    | <b>Power Supply Input.</b> Connect to the positive terminal of the Li+ cell through a decoupling network.                                                                                                                                                                                                                       |

| SS          | 11,12,13 | F3    | <b>Device Ground.</b> Connect directly to the negative terminal of the Li+ cell.<br>For the external sense resistor configuration, connect the sense resistor<br>between VSS and SNS.                                                                                                                                           |

| NS          | 4,5,6    | A3    | Sense Resistor Connection. Connect to the negative terminal of the battery pack. In the internal sense resistor configuration, the sense resistor is connected between VSS and SNS.                                                                                                                                             |

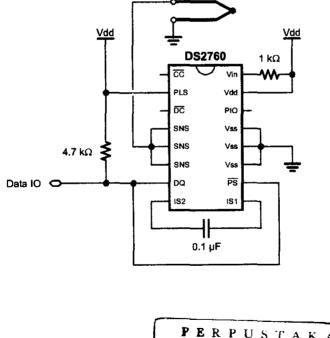

| S1          | 9        | D4    | Current Sense Input. This pin is internally connected to VSS through a $4.7k\Omega$ resistor. Connect a $0.1\mu$ F capacitor between IS1 and IS2 to complete a low-pass input filter.                                                                                                                                           |

| S2          | 8        | C4    | Current Sense Input. This pin is internally connected to SNS through a $4.7k\Omega$ resistor.                                                                                                                                                                                                                                   |

| NS<br>obe   | N/A      | C2    | Do Not Connect.                                                                                                                                                                                                                                                                                                                 |

| 'SS<br>robe | N/A      | D2    | Do Not Connect.                                                                                                                                                                                                                                                                                                                 |

chanical drawing for the 16-pin TSSOP and DS2760 flip-chip package can be found at: /pdfserv.maxim-ic.com/arpdf/Packages/16tssop.pdf /pdfserv.maxim-ic.com/arpdf/Packages/chips/2760x.pdf

SENS is present for external sense resistor configurations only SENSINT is present for internal sense resistor configurations only

#### ER MODES

S2760 has two power modes: Active and Sleep. While in Active Mode, the DS2760 continually res current, voltage and temperature to provide data to the host system and to support current ulation and Li+ safety monitoring. In Sleep Mode, the DS2760 ceases these activities. The 0 enters Sleep Mode when any of the following conditions occurs:

PMOD bit in the Status Register has been set to 1 and the DQ line is low for longer than econds (pack disconnection)

voltage on VIN drops below undervoltage threshold V<sub>UV</sub> for t<sub>UVD</sub> (cell depletion)

pack is disabled through the issuance of a SWAP command (SWEN bit =1)

S2760 returns to Active Mode when any of the following occurs:

PMOD bit has been set to 1 and the SWEN bit is set to 0 and the DQ line is pulled high ick connection)

$\rightarrow$  PS pin is pulled low (power switch)

voltage on PLS becomes greater than the voltage on VIN (charger connection) with the SWEN bit : to 0

pack is enabled through the issuance of a SWAP command (SWEN bit =1)

S2760 defaults to Sleep Mode when power is first applied.

#### **PROTECTION CIRCUITRY**

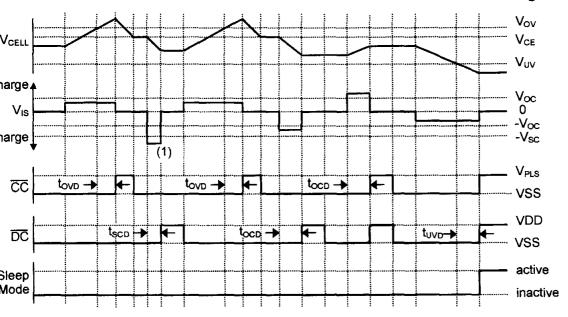

g Active Mode, the DS2760 constantly monitors cell voltage and current to protect the battery from narge (overvoltage), overdischarge (undervoltage) and excessive charge and discharge currents current, short circuit). Conditions and DS2760 responses are described in the sections below and arized in Table 2 and Figure 3.

| rutection conditions and ds2760 responses table 2 |                                 |                  |                                        |                                                 |  |

|---------------------------------------------------|---------------------------------|------------------|----------------------------------------|-------------------------------------------------|--|

| dition                                            | Activation                      |                  |                                        | Release                                         |  |

| le                                                | Threshold                       | Delay            | Response                               | Threshold                                       |  |

| voltage                                           | $VIN > V_{OV}$                  | tovD             | CC high                                | VIN < V <sub>CE</sub>                           |  |

| ervoltage                                         | $VIN < V_{UV}$                  | t <sub>UVD</sub> | CC, DC high,       Sleep Mode          | $V_{PLS} > V_{DD}^{(1)}$<br>(charger connected) |  |

| current, Charge                                   | $V_{\rm IS} > V_{\rm OC}^{(2)}$ | tocd             | $\overline{CC}$ , $\overline{DC}$ high | $V_{\rm PLS} < V_{\rm DD} - V_{\rm TP}^{(3)}$   |  |

| current, Discharge                                | $V_{IS} < -V_{OC}^{(2)}$        | tocD             | DC high                                | $V_{PLS} > V_{DD} - V_{TP}^{(4)}$               |  |

| t Circuit                                         | $V_{SNS} > V_{SC}$              | t <sub>SCD</sub> | DC high                                | $V_{PLS} > V_{DD} - V_{TP}^{(4)}$               |  |

#### PROTECTION CONDITIONS AND DS2760 RESPONSES Table 2

$V_{IS1} - V_{IS2}$ . Logic high =  $V_{PLS}$  for  $\overline{CC}$  and  $V_{DD}$  for  $\overline{DC}$ . All voltages are with respect to VSS. I<sub>SNS</sub> nces current delivered from pin SNS.

$V_{DD}$  <2.2V, release is delayed until the recovery charge current (I<sub>RC</sub>) passed from PLS to  $V_{DD}$  arges the battery and allows  $V_{DD}$  to exceed 2.2V.

r the internal sense resistor configuration, the overcurrent thresholds are expressed in terms of urrent:  $I_{SNS} > I_{OC}$  for charge direction and  $I_{SNS} < -I_{OC}$  for discharge direction ith test current  $I_{TST}$  current flowing from PLS to VSS (pull-down on PLS)

ith test current  $I_{TST}$  current flowing from  $V_{DD}$  to PLS (pull-up on PLS)

voltage. If the voltage of the cell exceeds overvoltage threshold  $V_{OV}$  for a period longer than oltage delay  $t_{OVD}$ , the DS2760 shuts off the external charge FET and sets the OV flag in the ction Register. When the cell voltage falls below charge enable threshold  $V_{CE}$ , the DS2760 turns the

FET back on (unless another protection condition prevents it). Discharging remains enabled overvoltage.

**voltage.** If the voltage of the cell drops below undervoltage threshold  $V_{UV}$  for a period longer than oltage delay  $t_{UVD}$ , the DS2760 shuts off the charge and discharge FETs, sets the UV flag in the tion Register, and enters Sleep Mode. The DS2760 provides a current-limited (I<sub>RC</sub>) recovery path from PLS to VDD to gently charge severely depleted cells. The recovery path is enabled  $0 \le VDD < 3V(typ)$ . Once VDD reaches 3V(typ), the DS2760 will return to normal operation, 1g connection of a charger to turn on the charge FET and pull out of Sleep Mode.

**urrent, Charge Direction.** The voltage difference between the IS1 pin and the IS2 pin ( $V_{IS} = V_{IS1}$ ) is the filtered voltage drop across the current sense resistor. If  $V_{IS}$  exceeds overcurrent threshold r a period longer than overcurrent delay  $t_{OCD}$ , the DS2760 shuts off both external FETs and sets the lag in the Protection Register. The charge current path is not re-established until the voltage on the in drops below  $V_{DD} - V_{TP}$ . The DS2760 provides a test current of value  $I_{TST}$  from PLS to VSS to LS down in order to detect the removal of the offending charge current source.

current, Discharge Direction. If  $V_{IS}$  is less than  $-V_{OC}$  for a period longer than  $t_{OCD}$ , the DS2760 off the external discharge FET and sets the DOC flag in the Protection Register. The discharge t path is not re-established until the voltage on PLS rises above  $V_{DD} - V_{TP}$ . The DS2760 provides a urrent of value  $I_{TST}$  from  $V_{DD}$  to PLS to pull PLS up in order to detect the removal of the offending npedance load.

**Circuit.** If the voltage on the SNS pin with respect to VSS exceeds short circuit threshold  $V_{SC}$  for od longer than short circuit delay  $t_{SCD}$ , the DS2760 shuts off the external discharge FET and sets the flag in the Protection Register. The discharge current path is not re-established until the voltage on ises above  $V_{DD} - V_{TP}$ . The DS2760 provides a test current of value  $I_{TST}$  from  $V_{DD}$  to PLS to pull p in order to detect the removal of the short circuit.

#### IUM-ION PROTECTION CIRCUITRY EXAMPLE WAVEFORMS Figure 3

<sup>(1)</sup> To allow the device to react quickly to short circuits, detection is actually done on the SNS pin rather than on the filtered IS1 and IS2 pins. The actual short circuit detect condition is  $V_{SNS} > V_{SC}$ .

**ary.** All of the protection conditions described above are OR'ed together to affect the  $\overline{CC}$  and  $\overline{DC}$  s.

$\overline{DC}$  = (Undervoltage) or (Overcurrent, EITHER Direction) or (Short Circuit) or (Protection Register bit DE = 0) or (Sleep Mode)

$\overline{\text{CC}}$  = (Overvoltage) or (Undervoltage) or (Overcurrent, Charge Direction) or (Protection Register bit CE = 0) or (Sleep Mode)

#### **RENT MEASUREMENT**

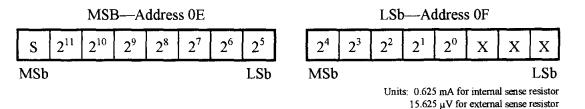

Active Mode of operation, the DS2760 continually measures the current flow into and out of the y by measuring the voltage drop across a current sense resistor. The DS2760 is available in two surations: (1) internal 25m $\Omega$  current sense resistor, and (2) external user-selectable sense resistor. In configuration, the DS2760 considers the voltage difference between pins IS1 and IS2 (V<sub>IS</sub> = V<sub>IS1</sub> – to be the filtered voltage drop across the sense resistor. A positive V<sub>IS</sub> value indicates current is 1g into the battery (charging), while a negative V<sub>IS</sub> value indicates current is flowing out of the y (discharging).

measured with a signed resolution of 12-bits. The current register is updated in two's complement t every 88ms (128/fsample) with an average of 128 readings. Currents outside the range of the er are reported at the limit of the range. The format of the Current Register is shown in Figure 4.

the internal sense resistor configuration, the DS2760 maintains the Current Register in units of Amps, a resolution of 0.625mA and full scale range of no less than  $\pm 1.9A$  (see Note 7 on I<sub>FS</sub> spec for more s). The DS2760 automatically compensates for internal sense resistor process variations and erature effects when reporting current.

the external sense resistor configuration, the DS2760 writes the measured  $V_{IS}$  voltage to the Current ter, with a resolution of  $15.625\mu V$  and a full scale range of  $\pm 64m V$ .

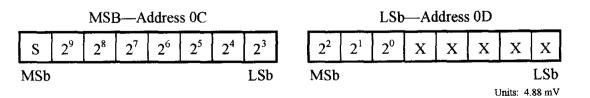

#### RENT REGISTER FORMAT Figure 4

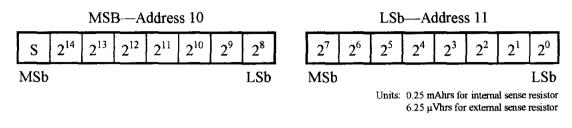

#### RENT ACCUMULATOR

Current Accumulator facilitates remaining capacity estimation by tracking the net current flow into ut of the battery. Current flow into the battery increments the Current Accumulator while current out of the battery decrements it. Data is maintained in the Current Accumulator in two'slement format. The format of the Current Accumulator is shown in Figure 5.

the internal sense resistor is used, the DS2760 maintains the Current Accumulator in units of Amp, with a resolution of 0.25mAhrs and full scale range of  $\pm 8.2$ Ahrs. When using an external sense

r, the DS2760 maintains the Current Accumulator in units of Volt-hours, with a resolution of Vhrs and a full scale range of  $\pm 205$  mVhrs.

urrent Accumulator is a read/write register that can be altered by the host system as needed.

#### **RENT ACCUMULATOR FORMAT** Figure 5

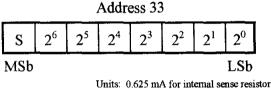

#### RENT OFFSET COMPENSATION

nt measurement and the current accumulation are both internally compensated for offset on a nual basis minimizing error resulting from variations in device temperature and voltage. ionally a constant bias may be utilized to alter any other sources of offset. This bias resides in OM address 33h in two's-complement format and is subtracted from each current measurement. current offset bias is applied to both the internal and external sense resistor configurations. The y default for the current offset compensation is a value of 0.

#### RENT OFFSET BIAS Figure 6

15.625 uV for external sense resistor

#### TAGE MEASUREMENT

DS2760 continually measures the voltage between pins VIN and VSS over a range of 0 to 4.75V. resulting data is placed in the Voltage Register in two's-complement format with a resolution of nV. Voltages above the maximum register value are reported as the maximum value. The Voltage ter format is shown in Figure 7.

#### TAGE REGISTER FORMAT Figure 7

#### PERATURE MEASUREMENT

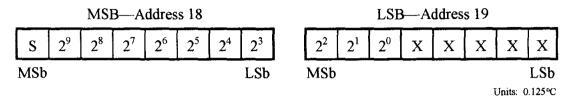

)S2760 uses an integrated temperature sensor to continually measure battery temperature. rature measurements are placed in the Temperature Register in two's-complement format with a ion of  $0.125^{\circ}$ C over a range of  $\pm 127^{\circ}$ C. The Temperature Register format is shown in Figure 8.

## PERATURE REGISTER FORMAT Figure 8

#### **GRAMMABLE I/O**

e the PIO pin as an output, write the desired output value to the PIO bit in the Special Feature er. Writing a 0 to the PIO bit enables the PIO output driver, pulling the PIO pin to VSS. Writing a re PIO bit disables the output driver, allowing the PIO pin to be pulled high or used as an input. To the value on the PIO pin, read the PIO bit. The DS2760 turns off the PIO output driver and sets the igh when it enters Sleep Mode or when DQ is low for more than 2 seconds, regardless of the state PMOD bit.

## VER SWITCH INPUT

DS2760 provides a power control function that uses the discharge protection FET to gate battery is to the system. The  $\overline{PS}$  pin, internally pulled to V<sub>DD</sub> through a 1µA current source, is continuously ored for a low-impedance connection to VSS. If the DS2760 is in Sleep Mode, the detection of a n  $\overline{PS}$  causes the device to transition into Active Mode, turning on the discharge FET. If the DS2760 eady in Active Mode, activity on  $\overline{PS}$  has no effect other than the mirroring of its logic level in the t in the Special Feature Register. The reading of a 0 in the  $\overline{PS}$  bit should be immediately followed iting a 1 to the  $\overline{PS}$  bit to ensure proper operation.

#### IORY

DS2760 has a 256-byte linear address space with registers for instrumentation, status and control in ower 32 bytes, with lockable EEPROM and SRAM memory occupying portions of the remaining ss space. All EEPROM and SRAM memory is general-purpose except addresses 30h, 31h, and 33h, a should be written with the default values for the Protection Register, Status Register, and Current t Register, respectively. When the MSB of any 2-byte register is read, both the MSB and LSB are ad and held for the duration of the Read Data command to prevent updates during the read and e synchronization between the two register bytes. For consistent results, always read the MSB and SB of a two-byte register during the same Read Data command sequence.

COM memory is shadowed by RAM to eliminate programming delays between writes and to allow that to be verified by the host system before being copied to EEPROM. All reads and writes to/from COM memory actually access the shadow RAM. In unlocked EEPROM blocks, the Write Data and updates shadow RAM. In locked EEPROM blocks, the Write Data command is ignored. The Data command copies the contents of shadow RAM to EEPROM in an unlocked block of COM but has no effect on locked blocks. The Recall Data command copies the contents of a block of COM to shadow RAM regardless of whether the block is locked or not.

## **ORY MAP** Table 3

| ldress (Hex) | Description                      | Read/Write |  |  |  |

|--------------|----------------------------------|------------|--|--|--|

| 00           | Protection Register              | R/W        |  |  |  |

| 01           | Status Register                  | R          |  |  |  |

| 02-06        | Reserved                         |            |  |  |  |

| 07           | EEPROM Register                  | R/W        |  |  |  |

| 08           | Special Feature Register         | R/W        |  |  |  |

| 09-0B        | Reserved                         |            |  |  |  |

| 0C           | Voltage Register MSb             | R          |  |  |  |

| 0D           | Voltage Register LSb             | R          |  |  |  |

| 0E           | Current Register MSB             | R          |  |  |  |

| 0F           | Current Register LSb             | R          |  |  |  |

| 10           | Accumulated Current Register MSB | R/W        |  |  |  |

| 11           | Accumulated Current Register LSb | R/W        |  |  |  |

| 12-17        | Reserved                         |            |  |  |  |

| 18           | Temperature Register MSB         | R          |  |  |  |

| 19           | Temperature Register LSb         | R          |  |  |  |

| 1A-1F        | Reserved                         |            |  |  |  |

| 20-2F        | EEPROM, block 0                  |            |  |  |  |

| 30-3F        | EEPROM, block 1                  |            |  |  |  |

| 40-7F        | Reserved                         |            |  |  |  |

| 80-8F        | SRAM R/                          |            |  |  |  |

| 90-FF        | Reserved                         |            |  |  |  |

EEPROM block is read/write until locked by the LOCK command, after which it is read-only.

#### TECTION REGISTER

Protection Register consists of flags that indicate protection circuit status and switches that give tional control over the charging and discharging paths. Bits OV, UV, COC and DOC are set when sponding protection conditions occur and remain set until cleared by the host system. The default s of the CE and DE bits of the Protection Register are stored in lockable EEPROM in the sponding bits in address 30h. A Recall Data command for EEPROM block 1 recalls the default s of 1 into CE and DE. The format of the Protection Register is shown in Figure 9. The function of bit is described in detail in the following paragraphs.

## TECTION REGISTER FORMAT Figure 9

|       |       |       | Addre        | ess 00       |       |              |              |

|-------|-------|-------|--------------|--------------|-------|--------------|--------------|

| bit 7 | bit 6 | bit 5 | <u>bit 4</u> | <u>bit 3</u> | bit 2 | <u>bit 1</u> | <u>bit 0</u> |

| OV    | UV    | COC   | DOC          | CC           | DC    | CE           | DE           |

Overvoltage Flag. When set to 1, this bit indicates the battery pack has experienced an overvoltage tion. This bit must be reset by the host system.

- Undervoltage Flag. When set to 1, this bit indicates the battery pack has experienced an voltage condition. This bit must be reset by the host system.

- Charge Overcurrent Flag. When set to 1, this bit indicates the battery pack has experienced a -direction overcurrent condition. This bit must be reset by the host system.

- Discharge Overcurrent Flag. When set to 1, this bit indicates the battery pack has experienced a rge-direction overcurrent condition. This bit must be reset by the host system.

$\overline{CC}$  Pin Mirror. This read-only bit mirrors the state of the  $\overline{CC}$  output pin.

$\overline{DC}$  Pin Mirror. This read-only bit mirrors the state of the  $\overline{DC}$  output pin.

Charge Enable. Writing a 0 to this bit disables charging ( $\overline{CC}$  output high, external charge FET off) less of cell or pack conditions. Writing a 1 to this bit enables charging, subject to override by the ice of any protection conditions. The DS2760 automatically sets this bit to 1 when it transitions sleep Mode to Active Mode.

Discharge Enable. Writing a 0 to this bit disables discharging ( $\overline{DC}$  output high, external discharge off) regardless of cell or pack conditions. Writing a 1 to this bit enables discharging, subject to de by the presence of any protection conditions. The DS2760 automatically sets this bit to 1 when sitions from Sleep Mode to Active Mode.

#### TUS REGISTER

lefault values for the Status Register bits are stored in lockable EEPROM in the corresponding bits dress 31h. A Recall Data command for EEPROM block 1 recalls the default values into the Status ter bits. The format of the Status Register is shown in Figure 10. The function of each bit is ibed in detail in the following paragraphs.

#### TUS REGISTER FORMAT Figure 10

Address 01

| <u>bit 7</u> | bit 6 | bit 5 | <u>bit 4</u> | bit_3 | bit 2_ | <u>bit 1</u> | <u>bit 0</u> |

|--------------|-------|-------|--------------|-------|--------|--------------|--------------|

| X            | X     | PMOD  | RNAOP        | SWEN  | X      | X            | X            |

D - Sleep Mode Enable. A value of 1 in this bit enables the DS2760 to enter Sleep Mode when the ine goes low for greater than 2 seconds and leave Sleep Mode when the DQ line goes high. A value disables DQ-related transitions into and out of Sleep Mode. This bit is read-only. The desired lt value should be set in bit 5 of address 31h. The factory default is 0.

OP – Read Net Address Opcode. A value of 0 in this bit sets the opcode for the Read Net Address nand to 33h, while a 1 sets the opcode to 39h. This bit is read-only. The desired default value should t in bit 4 of address 31h. The factory default is 0.

N - SWAP Command Enable. A value of 1 in this bit location enables the recognition of a SWAP nand. If set to 0, SWAP commands are ignored. The desired default value should be set in bit 3 of set 31h. This bit is read-only. The factory default is 0.

Reserved bits.

#### **ROM REGISTER**

rmat of the EEPROM Register is shown in Figure 11. The function of each bit is described in in the following paragraphs.

#### **ROM REGISTER FORMAT** Figure 11

| Address | 07 |  |

|---------|----|--|

|         |    |  |

| <u>bit 7</u> | <u>bit 6</u> | bit 5 | <u>bit 4</u> | bit 3 | bit 2 | bit 1 | <u>bit 0</u> |

|--------------|--------------|-------|--------------|-------|-------|-------|--------------|

| EEC          | LOCK         | X     | X            | X     | X     | BL1   | BL0          |

- EEPROM Copy Flag. A 1 in this read-only bit indicates that a Copy Data command is in 25. While this bit is high, writes to EEPROM addresses are ignored. A 0 in this bit indicates that 14 be written to unlocked EEPROM blocks.

K – EEPROM Lock Enable. When this bit is 0, the Lock command is ignored. Writing a 1 to this ables the Lock command. After the Lock command is executed, the LOCK bit is reset to 0. The y default is 0.

- EEPROM Block 1 Lock Flag. A 1 in this read-only bit indicates that EEPROM Block 1 esses 30-3F) is locked (read-only) while a 0 indicates Block 1 is unlocked (read/write).

- EEPROM Block 0 Lock Flag. A 1 in this read-only bit indicates that EEPROM Block 0 esses 20-2F) is locked (read-only) while a 0 indicates Block 0 is unlocked (read/write).

Reserved bits.

#### CIAL FEATURE REGISTER

format of the Special Feature Register is shown in Figure 12. The function of each bit is described in in the following paragraphs.

#### CIAL FEATURE REGISTER FORMAT Figure 12

| Address 08 |              |       |       |       |       |               |       |

|------------|--------------|-------|-------|-------|-------|---------------|-------|

| bit 7      | <u>bit 6</u> | bit 5 | bit 4 | bit 3 | bit 2 | _bit <u>1</u> | bit 0 |

| PS         | PIO          | MSTR  | Х     | X     | X     | X             | X     |

- PS Pin Mirror. This read-only bit mirrors the state of the PS pin. The reading of a 0 in this bit d be immediately followed by writing a 1 to this location to insure proper operation.

- PIO Pin Sense and Control. See the Programmable I/O section for details on this read/write bit.

$\mathbf{R}$  - SWAP Master Status Bit. This bit indicates whether a device has been selected through the P command. Selection of this device through the SWAP command and the appropriate Net Address result in setting this bit, indicating that this device is the master. A 0 signifies that this device is not naster.

Reserved bits.

#### **RE BUS SYSTEM**

Wire bus is a system which has a single bus master and one or more slaves. A multidrop bus is a s bus with multiple slaves. A single-drop bus has only one slave device. In all instances, the 50 is a slave device. The bus master is typically a microprocessor in the host system. The sion of this bus system consists of four topics: 64-Bit Net Address, Hardware Configuration, action Sequence, and 1-Wire Signaling.

#### **IT NET ADDRESS**

DS2760 has a unique, factory-programmed 1-Wire net address which is 64 bits in length. The first are the 1-Wire family code (30h for DS2760). The next 48 bits are a unique serial number. The bits are a CRC of the first 56 bits (see Figure 13). The 64-bit net address and the 1-Wire I/O try built into the device enable the DS2760 to communicate via the 1-Wire protocol detailed in the *e Bus System* section of this data sheet.

## **RE NET ADDRESS FORMAT** Figure 13

| 8-bit CRC | 48-bit Serial Number | 8-Bit Family Code 30h) |

|-----------|----------------------|------------------------|

| MSb       |                      | LSb                    |

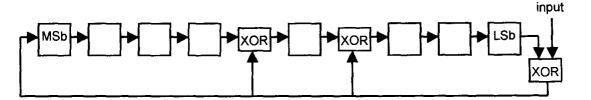

#### ; GENERATION

DS2760 has an 8-bit CRC stored in the most significant byte of its 1-Wire net address. To ensure free transmission of the address, the host system can compute a CRC value from the first 56 bits of ldress and compare it to the CRC from the DS2760. The host system is responsible for verifying the value and taking action as a result. The DS2760 does not compare CRC values and does not ent a command sequence from proceeding as a result of a CRC mismatch. Proper use of the CRC esult in a communication channel with a very high level of integrity.

CRC can be generated by the host using a circuit consisting of a shift register and XOR gates as n in Figure 10, or it can be generated in software. Additional information about the Dallas 1-Wire c Redundancy Check is available in Application Note 27 entitled "Understanding and Using Cyclic indancy Checks with Dallas Semiconductor Touch Memory Products". (This application note can be 1 on the Maxim/Dallas Semiconductor website at www.maxim-ic.com).

e circuit in Figure 14, the shift register bits are initialized to 0. Then, starting with the least ficant bit of the family code, one bit at a time is shifted in. After the  $8^{th}$  bit of the family code has entered, then the serial number is entered. After the  $48^{th}$  bit of the serial number has been entered, nift register contains the CRC value.

## **RE CRC GENERATION BLOCK DIAGRAM** Figure 14

#### DWARE CONFIGURATION

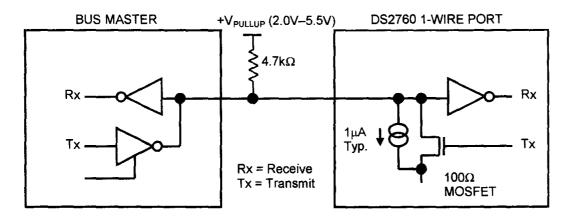

ise the 1-Wire bus has only a single line, it is important that each device on the bus be able to drive ne appropriate time. To facilitate this, each device attached to the 1-Wire bus must connect to the ith open-drain or tri-state output drivers. The DS2760 used an open-drain output driver as part of directional interface circuitry shown in Figure 15. If a bidirectional pin is not available on the bus r, separate output and input pins can be tied together.

-Wire bus must have a pull-up resistor at the bus-master end of the bus. For short line lengths, the of this resistor should be approximately  $5k\Omega$ . The idle state for the 1-Wire bus is high. If, for any n, a bus transaction must be suspended, the bus MUST be left in the idle state in order to properly 1e the transaction later. If the bus is left low for more than  $120\mu s$ , slave devices on the bus begin to ret the low period as a Reset Pulse, effectively terminating the transaction.

## IRE BUS INTERFACE CIRCUITRY Figure 15

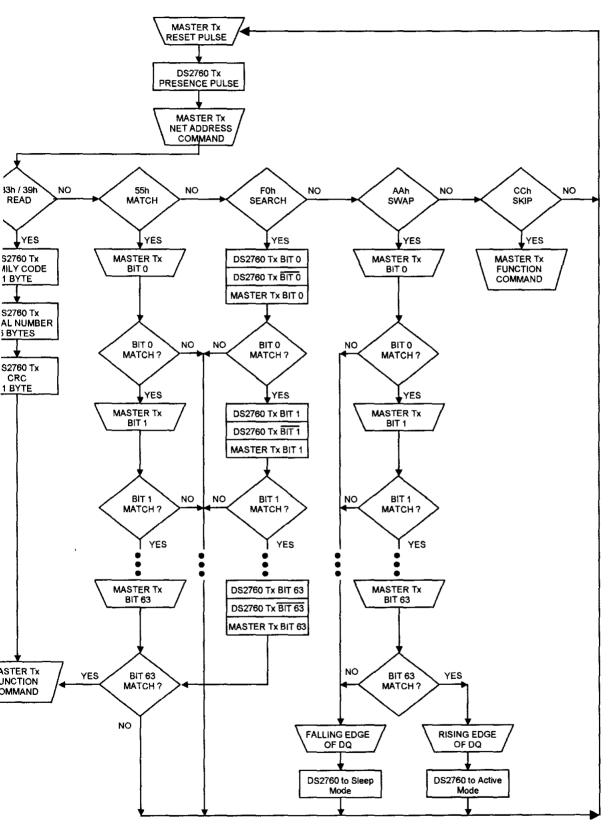

## **NSACTION SEQUENCE**

protocol for accessing the DS2760 via the 1-Wire port is as follows:

nitialization let Address Command unction Command ransaction/Data

sections that follow describe each of these steps in detail.

insactions of the 1-Wire bus begin with an initialization sequence consisting of a Reset Pulse itted by the bus master followed by a presence pulse simultaneously transmitted by the DS2760 y other slaves on the bus. The presence pulse tells the bus master that one or more devices are on s and ready to operate. For more details, see the *1-Wire Signaling* section.

#### ADDRESS COMMANDS

the bus master has detected the presence of one or more slaves, it can issue one of the Net Address lands described in the following paragraphs. The name of each ROM Command is followed by the opcode for that command in square brackets. Figure 16 presents a transaction flowchart of the Net iss Commands.

Net Address [33h or 39h]. This command allows the bus master to read the DS2760's 1-Wire net ss. This command can only be used if there is a single slave on the bus. If more than one slave is it, a data collision occurs when all slaves try to transmit at the same time (open-drain produces a -AND result). The RNAOP bit in the Status Register selects the opcode for this command, with DP=0 indicating 33h and RNAOP=1 indicating 39h.

**h** Net Address [55h]. This command allows the bus master to specifically address one DS2760 on Wire bus. Only the addressed DS2760 responds to any subsequent Function Command. All other devices ignore the Function Command and wait for a reset pulse. This command can be used with r more slave devices on the bus.

**Net Address [CCh].** This command saves time when there is only one DS2760 on the bus by ing the bus master to issue a Function Command without specifying the address of the slave. If than one slave device is present on the bus, a subsequent Function Command can cause a data ion when all slaves transmit data at the same time.

ch Net Address [F0h]. This command allows the bus master to use a process of elimination to ify the 1-Wire net addresses of all slave devices on the bus. The search process involves the ition of a simple three-step routine: read a bit, read the complement of the bit, then write the desired of that bit. The bus master performs this simple three-step routine on each bit location of the net ess. After one complete pass through all 64 bits, the bus master knows the address of one device. remaining devices can then be identified on additional iterations of the process. See Chapter 5 of the of  $DS19xx \ iButton^{\ensuremath{\mathbb{R}}}$  Standards for a comprehensive discussion of a net address search, including an 1 example. (This publication can be found on the Maxim/Dallas Semiconductor website at maxim-ic.com).

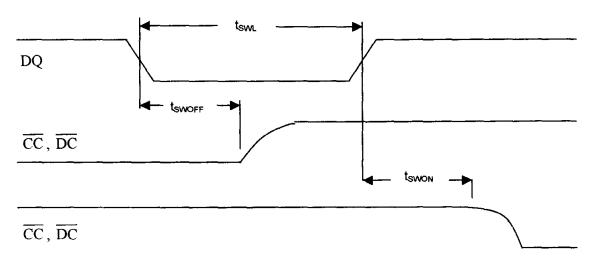

**P** [AAh]. SWAP is a Net Address level command specifically intended to aid in distributed plexing applications and is described specifically with regards to power control using the 27xx series oducts. The term power control refers to the ability of the DS2760 to control the flow of power into at the battery pack using control pins  $\overline{DC}$  and  $\overline{CC}$ . The SWAP command is issued followed by the Address. The effect is to cause the addressed device to enable power to or from the system while taneously (break-before-make) deselecting and powering down (SLEEP) all other packs. This hing sequence is controlled by a timing pulse issued on the DQ line following the net address. The g edge of the pulse is used to disable power with the rising edge enabling power flow by the selected we. The DS2760 will recognize a SWAP command, device address, and timing pulse if and only if WEN bit is set.

is a registered trademark of Dallas Semiconductor.

#### **CTION COMMANDS**

successfully completing one of the Net Address Commands, the bus master can access the features DS2760 with any of the Function Commands described in the following paragraphs. The name of inction is followed by the 8-bit opcode for that command in square brackets.

**Data [69h, XX].** This command reads data from the DS2760 starting at memory address XX. The f the data in address XX is available to be read immediately after the MSb of the address has been d. Because the address is automatically incremented after the MSb of each byte is received, the f the data at address XX+1 is available to be read immediately after the MSb of the data at address lf the bus master continues to read beyond address FFh, the DS2760 outputs logic 1 until a Reset occurs. Addresses labeled "Reserved" in the Memory Map contain undefined data. The Read Data and may be terminated by the bus master with a Reset Pulse at any bit boundary.

**Data [6 Ch, XX].** This command writes data to the DS2760 starting at memory address XX. The f the data to be stored at address XX can be written immediately after the MSb of address has been d. Because the address is automatically incremented after the MSb of each byte is written, the LSb stored at address XX+1 can be written immediately after the MSb to be stored at address XX. If the laster continues to write beyond address FFh, the DS2760 ignores the data. Writes to read-only sses, reserved addresses and locked EEPROM blocks are ignored. Incomplete bytes are not written. s to unlocked EEPROM blocks are to shadow RAM rather than EEPROM. See the *Memory* section ore details.

**Data [48h, XX].** This command copies the contents of shadow RAM to EEPROM for the 16-byte COM block containing address XX. Copy Data commands that address locked blocks are ignored. If the Copy Data command is executing, the EEC bit in the EEPROM Register is set to 1 and writes PROM addresses are ignored. Reads and writes to non-EEPROM addresses can still occur while opy is in progress. The Copy Data command takes  $t_{EEC}$  time to execute, starting on the next falling after the address is transmitted.

**I Data [B8h, XX].** This command recalls the contents of the 16-byte EEPROM block containing ss XX to shadow RAM.

[6 Ah, XX]. This command locks (write-protects) the 16-byte block of EEPROM memory ining memory address XX. The LOCK bit in the EEPROM Register must be set to 1 before the command is executed. If the LOCK bit is 0, the Lock command has no effect. The Lock command manent; a locked block can never be written again.

| <b>ICTION</b> | COMMANDS Table 4                                                   |                     |                                     |                            |

|---------------|--------------------------------------------------------------------|---------------------|-------------------------------------|----------------------------|

| mmand         | Description                                                        | Command<br>Protocol | Bus State After<br>Command Protocol | Bus Data                   |

| ıd Data       | Reads data from memory<br>starting at address XX                   | 69h, XX             | Master Rx                           | up to 256 bytes<br>of data |

| ite Data      | Writes data to memory<br>starting at address XX                    | 6Ch, XX             | Master Tx                           | up to 256 bytes<br>of data |

| by Data       | Copies shadow RAM data<br>to EEPROM block<br>containing address XX | 48h, XX             | Bus Idle                            | none                       |

| all Data:     | Recalls EEPROM block<br>containing address XX to<br>shadow RAM     | B8h, XX             | Bus Idle                            | none                       |

| ж             | Permanently locks the<br>block of EEPROM<br>containing address XX  | 6Ah, XX             | Bus Idle                            | none                       |

## ADDRESS COMMAND FLOW CHART Figure 16

#### IGNALING

Wire bus requires strict signaling protocols to insure data integrity. The four protocols used by the 50 are: the initialization sequence (Reset Pulse followed by Presence Pulse), Write 0, Write 1, and Data. All of these types of signaling except the Presence Pulse are initiated by the bus master.

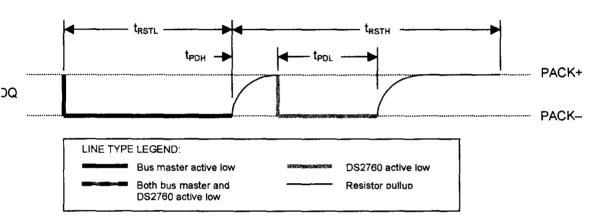

itialization sequence required to begin any communication with the DS2760 is shown in Figure 17. sence Pulse following a Reset Pulse indicates the DS2760 is read to accept a Net Address 1 and. The bus master transmits (Tx) a Reset Pulse for  $t_{RSTL}$ . The bus master then releases the line bes into receive mode (Rx). The 1-Wire bus line is then pulled high by the pull-up resistor. After ing the rising edge on the DQ pin, the DS2760 waits for  $t_{PDH}$  and then transmits the Presence Pulse  $t_{L}$ .

## **RE INITIALIZATION SEQUENCE** Figure 17

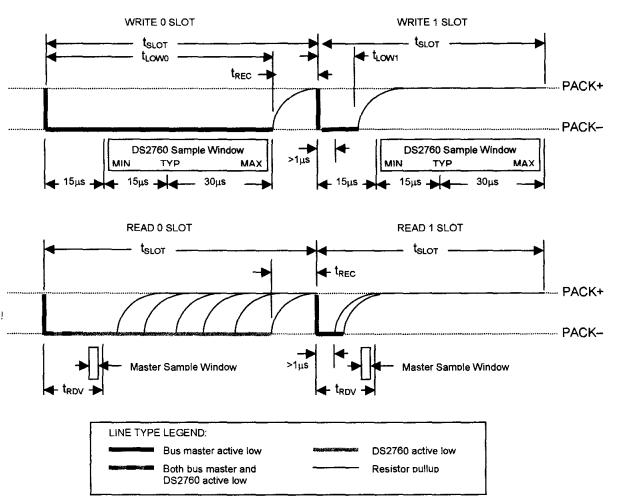

## TE TIME SLOTS

It time slot is initiated when the bus master pulls the 1-Wire bus from a logic high (inactive) level to c low level. There are two types of write time slots: Write 1 and Write 0. All write time slots must  $_{COT}$  (60µs to 120µs) in duration with a 1µs minimum recovery time,  $t_{REC}$ , between cycles. The 60 samples the 1-Wire bus line between 15µs and 60µs after the line falls. If the line is high when led, a Write 1 occurs. If the line is low when sampled, a Write 0 occurs (see Figure 18). For the bus r to generate a Write 1 time slot, the bus line must be pulled low and then released, allowing the line pulled high within 15µs after the start of the write time slot. For the host to generate a Write 0 time he bus line must be pulled low and held low for the duration of the write time slot.

## D TIME SLOTS

In time slot is initiated when the bus master pulls the 1-Wire bus line from a logic high level to a low level. The bus master must keep the bus line low for at least 1µs and then release it to allow the 60 to present valid data. The bus master can then sample the data  $t_{RDV}$  (15µs) from the start of the time slot. By the end of the read time slot, the DS2760 releases the bus line and allows it to be d high by the external pull-up resistor. All read time slots must be  $t_{SLOT}$  (60µs to 120µs) in duration a 1µs minimum recovery time,  $t_{REC}$ , between cycles. See Figure 18 for more information.

## RE WRITE AND READ TIME SLOTS Figure 18

## AP COMMAND TIMING Figure 19

## **OLUTE MAXIMUM RATINGS\***

$\frac{1}{2}$  e on PLS and  $\overline{CC}$  pin, Relative to VSS ge on PIO pin, Relative to VSS ze on VIN and  $\overline{PS}$ , Relative to VSS ge on any other pin, Relative to VSS uous Internal Sense Resistor Current 1 Internal Sense Resistor Current ting Temperature Range ze Temperature Range ring Temperature

-0.3V to +18V -0.3V to +12V -0.3V to  $V_{DD} + 0.3$ -0.3V to +6V +2.5A $\pm 50$ A for <100 µs/sec, <1000 pulses -40°C to +85°C -55°C to +125°C See IPC/JEDEC J-STD-020A Specification

is a stress rating only and functional operation of the device at these or any other conditions above e indicated in the operation sections of this specification is not implied. Exposure to absolute imum rating conditions for extended periods of time may affect reliability.

#### RATING AMETER

ly Voltage Pin

| <u> G</u> C( | ONDITIONS       |           | (-20°( | C to +7 | 70°C, 2 | .5V ≤ V <sub>D</sub> | <u>⊳ ≤ 5.5V)</u> |

|--------------|-----------------|-----------|--------|---------|---------|----------------------|------------------|

|              | SYMBOL          | CONDITION | MIN    | TYP     | MAX     | UNITS                | NOTES            |

|              | V <sub>DD</sub> |           | 2.5    |         | 5.5     | V                    | 1                |

|              | DQ              |           | -0.3   |         | 5.5     | V                    | 1                |

| ELECTRICAL (<br>AMETER     | SYMBOL              | CONDITION                        | MIN                    | TYP | MAX | UNITS | $\leq 5.5V$ )<br>NOTES |

|----------------------------|---------------------|----------------------------------|------------------------|-----|-----|-------|------------------------|

|                            |                     |                                  |                        |     |     | UNITS | HOTES                  |

| ve Current                 | I <sub>ACTIVE</sub> | $DQ = V_{DD},$                   |                        | 60  | 90  | μA    |                        |

|                            |                     | norm. operation                  |                        |     |     |       |                        |

| o Mode Current             | I <sub>SLEEP</sub>  | $\overline{DQ} = 0\overline{V},$ |                        | 1   | 2   | μA    |                        |

|                            |                     | no activity,                     |                        |     |     |       |                        |

|                            |                     | <b>PS</b> floating               | :                      | ĺ   |     |       |                        |

| t Logic High:              |                     |                                  | 1.5                    |     |     | V     | 1                      |

| PIO                        |                     |                                  |                        |     |     |       |                        |

| t Logic High: PS           | V <sub>IH</sub>     |                                  | $V_{DD}$ - 0.2V        |     |     | V     | 1                      |

| t Logic Low:               | V <sub>IL</sub>     |                                  |                        |     | 0.4 | V     | 1                      |

| PIO                        |                     |                                  |                        |     |     |       |                        |

| t Logic Low: PS            | VIL                 |                                  |                        |     | 0.2 | V     | 1                      |

| ut Logic High: CC          | V <sub>OH</sub>     | $I_{OH} = -0.1 \mathrm{mA}$      | $V_{PLS} - 0.4 V$      |     |     | V     | 1                      |

| ut Logic High: DC          | V <sub>OH</sub>     | $I_{OH} = -0.1 \text{ mA}$       | V <sub>DD</sub> - 0.4V |     |     | V     | 1                      |

| ut Logic Low:              | V <sub>OL</sub>     | $I_{OL} = 0.1 \text{mA}$         |                        |     | 0.4 | V     | 1                      |

| $, \overline{\mathrm{DC}}$ |                     |                                  |                        |     |     |       |                        |

| ut Logic Low:              | V <sub>OL</sub>     | $I_{OL} = 4mA$                   |                        |     | 0.4 | V     | 1                      |

| PIO                        |                     |                                  |                        |     |     |       |                        |

| Pulldown Current           | I <sub>PD</sub>     |                                  |                        | 1   |     | μA    |                        |

| t Resistance: VIN          | R <sub>IN</sub>     |                                  | 5                      |     |     | MΩ    |                        |

| nal Current Sense          | R <sub>SNS</sub>    | +25°C                            | 20                     | 25  | 30  | mΩ    |                        |

| stor                       |                     |                                  |                        |     |     |       |                        |

| Low to Sleep time          | t <sub>SLEEP</sub>  |                                  | 2.1                    | 1   |     | sec   |                        |

# **CTRICAL CHARACTERISTICS:**

|                      |                  | Ο.    |                                                                   |       |       |       |  |

|----------------------|------------------|-------|-------------------------------------------------------------------|-------|-------|-------|--|

| <b>TECTION CIRCU</b> | TRY              |       | $(0^{\circ}C \text{ to } +50^{\circ}C; 2.5V \le V_{DD} \le 5.5V)$ |       |       |       |  |

| AMETER               | SYMBOL           | MIN   | TYP                                                               | MAX   | UNITS | NOTES |  |

| voltage Detect       | Vov              | 4.325 | 4.350                                                             | 4.375 | V     | 1, 2  |  |

| _                    |                  | 4.250 | 4.275                                                             | 4.300 |       |       |  |

| ge Enable            | V <sub>CE</sub>  | 4.10  | 4.15                                                              | 4.20  | V     | 1     |  |

| rvoltage Detect      | V <sub>UV</sub>  | 2.5   | 2.6                                                               | 2.7   | V     | 1     |  |

| current Detect       | loc              | 1.8   | 1.9                                                               | 2.0   | A     | 3     |  |

| current Detect       | V <sub>oc</sub>  | 45    | 47.5                                                              | 50    | mV    | 1,4   |  |

| t Circuit Detect     | I <sub>SC</sub>  | 5.0   | 8.0                                                               | 11    | Α     | 3     |  |

| t Circuit Detect     | V <sub>SC</sub>  | 150   | 200                                                               | 250   | mV    | 1     |  |

| voltage Delay        | t <sub>OVD</sub> | 0.8   | 1                                                                 | 1.2   | sec   |       |  |

| ervoltage Delay      | t <sub>UVD</sub> | 90    | 100                                                               | 110   | ms    |       |  |

| current Delay        | t <sub>OCD</sub> | 5     | 10                                                                | 20    | ms    |       |  |

| t Circuit Delay      | t <sub>SCD</sub> | 80    | 100                                                               | 120   | μs    |       |  |

| Threshold            | V <sub>TP</sub>  | 0.5   | 1.0                                                               | 1.5   | V     |       |  |

| Current              | I <sub>TST</sub> | 10    | 20                                                                | 40    | μA    |       |  |

| overy Charge Current | I <sub>RC</sub>  | 0.5   | 1                                                                 | 2     | mA    | 13    |  |

|                      |                  |       |                                                                   |       |       |       |  |

|                                                                                                                  |                   |         |              |        |               | 0.02700       |

|------------------------------------------------------------------------------------------------------------------|-------------------|---------|--------------|--------|---------------|---------------|

| <b>CTRICAL CHARACTERISTICS:</b><br><b>PERATURE, VOLTAGE, CURRENT</b> (0°C to +50°C; $2.5V \le V_{DD} \le 5.5V$ ) |                   |         |              |        |               |               |

| AMETER                                                                                                           | SYMBOL            | MIN     |              | MAX    |               | <b>NOTES</b>  |

| perature Resolution                                                                                              | T <sub>LSB</sub>  | ·····   | 0.125        |        | °C            |               |

| perature Full Scale<br>nitude                                                                                    | T <sub>FS</sub>   | 127     |              |        | °C            |               |

| perature Error                                                                                                   | T <sub>ERR</sub>  |         |              | ±3     | °C            | 5             |

| age Resolution                                                                                                   | V <sub>LSB</sub>  |         | 4.88         |        | mV            |               |

| age Full Scale<br>nitude                                                                                         | V <sub>FS</sub>   | 4.75    |              |        | V             |               |

| age Offset Error                                                                                                 | VOERR             |         |              | 1      | LSB           | 6             |

| age Gain Error                                                                                                   | V <sub>GERR</sub> | <u></u> |              | 5      | %V<br>reading |               |

| ent Resolution                                                                                                   | I <sub>LSB</sub>  |         | 0.625        |        | mA<br>μV      | 3<br>4        |

| ent Full Scale<br>nitude                                                                                         | I <sub>FS</sub>   | 1.9     | 2.56<br>64   |        | A<br>mV       | 3, 7<br>4     |

| ent Offset Error                                                                                                 | I <sub>OERR</sub> |         |              | 1      | LSB           | 8             |

| ent Gain Error                                                                                                   | I <sub>GERR</sub> |         |              | 3<br>1 | %I<br>reading | 3, 9, 14<br>4 |

| umulated Current                                                                                                 | qca               |         | 0.25<br>6.25 |        | mAhr<br>μVhr  | 3<br>4        |

| ent Sampling<br>uency                                                                                            | f <sub>SAMP</sub> |         | 1456         |        | Hz            |               |

| mal Timebase Accuracy                                                                                            | t <sub>ERR</sub>  |         | ±1           | ±3     | %             | 10            |

24

# CTRICAL CHARACTERISTICS:<br/>RE INTERFACE $(-20^{\circ}C \text{ to } +70^{\circ}C; 2.5V \le V_{DD} \le 5.5V)$

| AMETER                             | SYMBOL             | MIN | TYP | MAX | UNITS | NOTES |

|------------------------------------|--------------------|-----|-----|-----|-------|-------|

| Slot                               | t <sub>SLOT</sub>  | 60  |     | 120 | μs    |       |

| very Time                          | t <sub>REC</sub>   | 1   |     |     | μs    |       |

| e 0 Low Time                       | t <sub>LOW0</sub>  | 60  |     | 120 | μs    |       |

| e 1 Low Time                       | t <sub>LOW1</sub>  | 1   |     | 15  | μs    |       |

| Data Valid                         | t <sub>RDV</sub>   |     |     | 15  | μs    |       |

| t Time High                        | t <sub>RSTH</sub>  | 480 |     |     | μs    |       |

| t Time Low                         | t <sub>RSTL</sub>  | 480 |     | 960 | μs    |       |

| ence Detect High                   | t <sub>PDH</sub>   | 15  |     | 60  | μs    |       |

| ence Detect Low                    | t <sub>PDL</sub>   | 60  |     | 240 | μs    |       |

| <b>\P</b> timing pulse width       | t <sub>SWL</sub>   | 0.2 |     | 120 | μs    |       |

| AP timing pulse                    | t <sub>swoff</sub> | 0   |     | 1   | μs    | 12    |

| $1g edge to \overline{DC} release$ |                    |     |     |     |       |       |

| AP timing pulse rising             | t <sub>swon</sub>  | 0   |     | 1   | μs    | 12    |

| to DC engage                       |                    |     |     |     |       |       |

| Capacitance                        | C <sub>DQ</sub>    |     |     | 60  | pF    |       |

|                                    |                    |     |     |     |       |       |

#### **ROM RELIABILITY SPECIFICATION** (-20°C to +70°C; $2.5V \le V_{DD} \le 5.5V$ )

|                    |                  |       | <u> </u> | ,   |        |       |