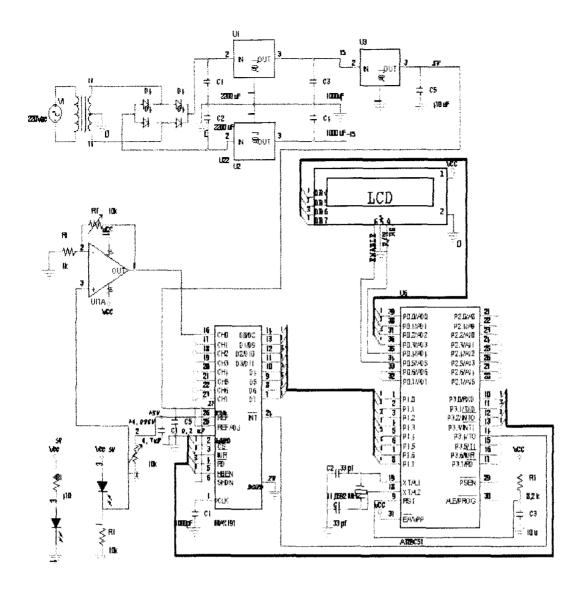

LAMPIRAN

```

ORG

H00

JMP

START

'** TURBIDITY **',0,'NTU',0

KATA:

DB

73,74,75,76,77,0

VALUE01:

DB

82,83,84,0

VALUE02:

DB

VALUE03:

89,90,91,92,93,0

DB

VALUE04:

DB

111,112,113,114,115,0

Delay 4 mS

D4mS:

MOV

R7,#29

R6,#64

D4mS01:

MOV

DJNZ

R6,$

DJNZ

R7,D4mS01

RET

Delay 1 S

D1S:

MOV

R7,#20

R6,#128

D1S01:

MOV

D1S02:

R5,#180

MOV

DJNZ

R5,$

DJNZ

R6,D1S02

R7,D1S01

DJNZ

RET

Enable Pulse Instruction

EPI:

ANL

A,#00FH

;4 Bit

;Enable High, Instruction Input

ORL

A,#0D0H

MOV

P0,A

;Enable Low, Instruction Input

ANL

A,#0CFH

MOV

P0,A

ACALL D4mS

;Delay 4 mS

```

RET

LCD Control Instruction

\$MOD51

**CSEG**

```

LCI:

MOV R5,A

;Ambil 4 Bit (D7..D4)

SWAP A

;Enable Pulse Instruction

ACALL EPI

;Ambil 4 Bit (D3..D0)

MOV A.R5

:Enable Pulse Instruction

ACALL EPI

RET

Inisialisasi LCD 4 Bit

MOV

R5.#3

:Diulang 3 Kali

IL4B:

IL4B01:

MOV

A,#03H

;Reset Sequence

:Enable Pulse Instruction

ACALL EPI

R5,IL4B01

DJNZ

MOV A,#02H

;Reset Sequence

Enable Pulse Instruction

ACALL EPI

;Function Set

MOV

A,#28H

;(4 Bit, 2 Lines, 5 x 7 Dot Matrik)

ACALL LCI

MOV

A.#06H

:Entry Mode Set

(Increment, No Display Shift)

ACALL LCI

;Display On/Off Control

MOV

A,#0CH

ACALL LCI

(Display On, Cursor Off, Blink Off)

Display Clear

MOV A,#01H

;LCD Control Instruction

ACALL LCI

RET

Enable Pulse Data

A,#00FH

;4 Bit

EPD:

ANL

A,#0F0H

ORL

Enable High, Data Input

MOV

P0,A

ANL

A,#0EFH

Enable Low, Data Input

MOV

P0,A

MOV R7,#40

;Delay 40 uS

DJNZ R7.$

RET

LCD Control Data

LCD:

MOV R5,A

SWAP A

;Ambil 4 Bit (D7..D4)

Enable Pulse Data

ACALL EPD

MOV A,R5

;Ambil 4 Bit (D3..D0)

```

```

RET

Tampilan Awal

MOV

A,#0

:Kirim Data ke LCD

KDKL:

MOVC

A,@A+DPTR

DPTR

INC

JZ

EscKDKL

;Huruf sudah habis?

;LCD Control Data

ACALL

LCD

JMP

KDKL

EscKDKL:

RET

;Cursor Home Line 1 Colom 0

TA:

MOV

A,#080H

:LCD Control Instruction

ACALL LCI

MOV DPTR.#KATA

:Kirim Data ke LCD

ACALL KDKL

A,#0C9H

;Cursor Home Line 2 Colom 9

MOV

;LCD Control Instruction

ACALL LCI

:Kirim Data ke LCD

ACALL KDKL

RET

Tampilkan Data ke LCD

;Cursor Home Line 2 Colom 3

TDKL:

MOV

A,#0C3H

ACALL LCI

;LCD Control Instruction

MOV

R0,#64H

TDKL01:

MOV

A,@R0

ADD

A,#30H

;Ubah menjadi kode ASCII

ACALL LCD

:LCD Control Data

DEC

R<sub>0</sub>

CJNE R0,#5FH,TDKL01

RET

Analog Digital Conversion

ADC:

CLR

P3.3

;Chip Select pin

CLR

P3.2

;Write pin

MOV

P1,#40H

P3.2

;Write pin

SETB

;Chip Select pin

P3.3

SETB

MOV

R7,#100

```

DJNZ R7,\$

ACALL EPD

Enable Pulse Data

```

MOV

P1,#0FFH

CLR

P3.3

;Chip Select pin

CLR P3.1

;Read pin

SETB P3.0

;HBEN pin

MOV

R4,P1

;4 MSB

CLR

P3.0

;HBEN pin

R3,P1

MOV

;8 LSB

;Read pin

SETB P3.1

SETB P3.3

;Chip Select pin

RET

Devision 16 bit

D16b:

CLR C

MOV

34H,#0

;Sisa bagi (LSB)

MOV

35H,#0

MOV

R7,#16

;Diulang 16 kali

D01:

MOV

R6,#4

MOV

R0,#32H

D02:

MOV

A,@R0

Α

RLC

;Geser ke kiri (35H 34H 33H 32H)

MOV @R0,A

INC

R0

R6,D02

DJNZ

MOV

A,34H

;Pengurangan

A,36H

ADD

MOV

38H,A

MOV

A,35H

ADDC

A,37H

MOV

39H,A

JC

D03

DJNZ

R7,D01

RET

D03:

CLR

C

A,32H

MOV

ORL A,#01H

MOV

32H,A

MOV

34H,38H

MOV

35H,39H

DJNZ

R7,D01

RET

```

```

Konversi Data ADC

CLR C

; R4 R3

KDA:

A,R3

; 00 43

MOV

SUBB A,#70

; ------

R3,A

; R4 R3

MOV

A,R4

MOV

A,#0

SUBB

R4,A

MOV

MOV R1,#2

;KDA00:

CLR C

A,R4

R4 R3

MOV

R4 R3 = -----

RRC

Α

MOV

R4,A

4

MOV

A,R3

RRC

Α

MOV

R3,A

DJNZ

R1,KDA00

MOV

32H,R3

MOV

33H,R4

MOV

36H,#018H

;Bagi 1000

MOV

37H,#0FCH

ACALL D16b

;Devision 16 bit

MOV

A,32H

JZ

KDA01

64H,A

MOV

KDA01:

MOV 32H,34H

33H,35H

MOV

MOV

36H,#09CH

;Bagi 100

MOV

37H_#0FFH

ACALL D16b

;Devision 16 bit

MOV

A,32H

JZ

KDA02

MOV

63H,A

KDA02:

MOV A,34H

MOV

B,#10

;Bagi 10

DIV

AB

MOV

62H,A

MOV

60H,B

RET

```

```

Cek Data

:Cek Value

MOV A,#0

CV:

MOVC A,@A+DPTR

JΖ

EscCV

INC DPTR

CJNE A,3H,CV

EscCV:

RET

MOV 64H,\#0F0H ;F0H + 30H = "" (ASCII)

CD:

F0H + 30H = " " (ASCII)

MOV

63H,#0F0H

CJNE R4,#0,CD05

CLR C

MOV

A,#70

SUBB A,R3

CD01

JC

MOV

62H,#0

MOV

60H,#0

RET

CD01:

MOV DPTR,#VALUE01

ACALL CV

;Cek Value

JΖ

CD02

MOV

62H,#0

MOV

60H,#2

RET

CD02:

MOV DPTR,#VALUE02

ACALL CV

;Cek Value

JZ

CD03

MOV

62H.#0

MOV

60H,#8

RET

CD03:

MOV DPTR.#VALUE03

ACALL CV

;Cek Value

JZ

CD04

MOV

62H,#3

MOV

60H,#6

RET

```

MOV DPTR,#VALUE04

;Cek Value

ACALL CV

JZ

CD05

CD04:

```

; Cek Data

```

CV: MOV A,#0 ;Cek Value

MOVC A,@A+DPTR

JZ EscCV INC DPTR CJNE A,3H,CV

EscCV: RET

CD: MOV 64H,#0F0H ; F0H + 30H = "" (ASCII)

MOV 63H,#0F0H ;F0H + 30H = " " (ASCII)

CJNE R4,#0,CD05

CLR C

MOV A,#70 SUBB A,R3 JC CD01 MOV 62H,#0 MOV 60H,#0

**RET**

CD01: MOV DPTR,#VALUE01

ACALL CV ;Cek Value

JZ CD02 MOV 62H,#0 MOV 60H,#2

**RET**

CD02: MOV DPTR,#VALUE02

ACALL CV ;Cek Value

JZ CD03 MOV 62H,#0 MOV 60H,#8

RET

CD03: MOV DPTR,#VALUE03

ACALL CV ;Cek Value

JZ CD04 MOV 62H,#3 MOV 60H,#6

**RET**

CD04: MOV DPTR,#VALUE04

ACALL CV ;Cek Value

JZ CD05

MOV 62H,#4 MOV 60H,#2

**RET**

CD05: ACALL KDA ;Konversi Data ADC

RET

7

Main Program

-----

START: MOV 61H,#0FEH ;FEH + 30H = "." (ASCII)

ACALL IL4B ;Inisialisasi LCD 4 Bit

ACALL TA ;Tampilan Awal

MP01: ACALL ADC

ACALL CD ;Cek Data

ACALL TDKL ;Tampilkan Data ke LCD

ACALL D1S ;Delay 1 S

JMP MP01

**END**

# LAMPIRAN B

# **Features**

- Compatible with MCS-51™ Products

- 4K Bytes of In-System Reprogrammable Flash Memory

- Endurance: 1,000 Write/Erase Cycles

- Fully Static Operation: 0 Hz to 24 MHz

- Three-Level Program Memory Lock

- 128 x 8-Bit Internal RAM

- 32 Programmable I/O Lines

- Two 16-Bit Timer/Counters

- · Six Interrupt Sources

- · Programmable Serial Channel

- Low Power Idle and Power Down Modes

# Description

The AT89C51 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of Flash Programmable and Erasable Read Only Memory (PEROM). The device is manufactured using Atmel's high density nonvolatile memory technology and is compatible with the industry standard MCS-51™ instruction set and pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C51 is a powerful microcomputer which provides a highly flexible and cost effective solution to many embedded control applications.

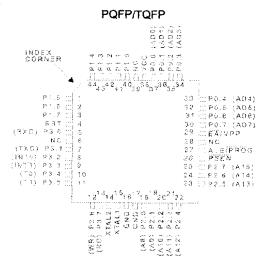

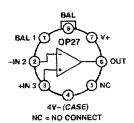

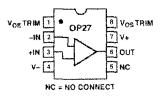

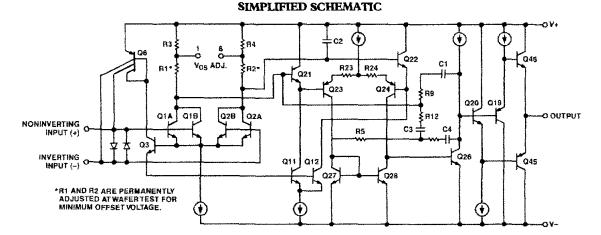

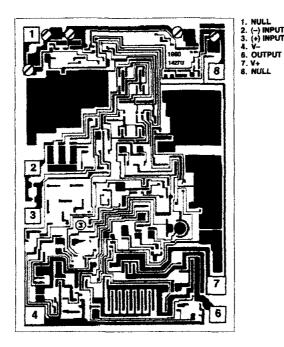

# **Pin Configurations**

# 8-Bit Microcontroller with 4K Bytes Flash

AT89C51

0265F-A-12/97

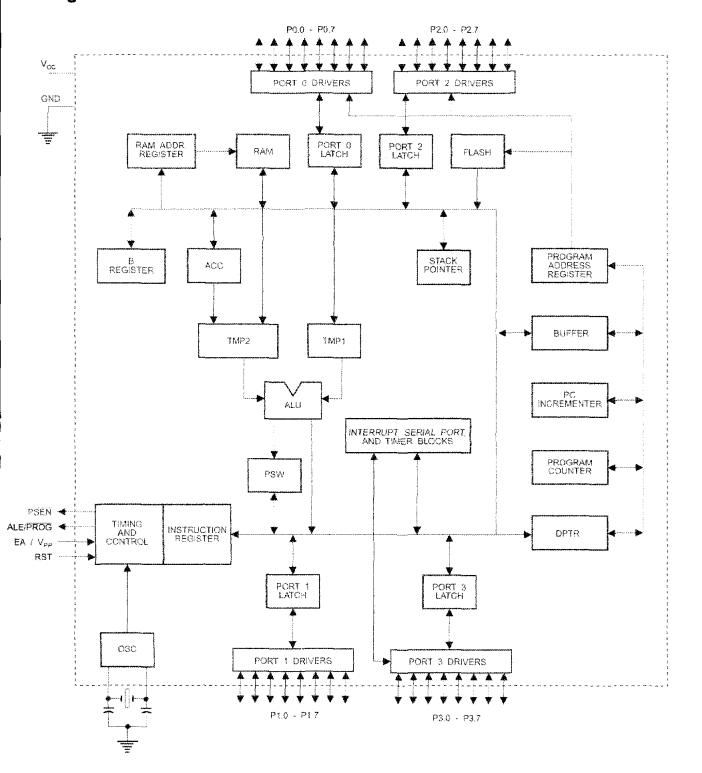

# lock Diagram

AT89C51

The AT89C51 provides the following standard features: 4K bytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator and clock circuitry. In addition, the AT89C51 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The Power Down Mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset.

# **Pin Description**

# V<sub>CC</sub>

Supply voltage.

### GND

Ground.

### Port 0

Port 0 is an 8-bit open drain bidirectional I/O port. As an output port each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs.

Port 0 may also be configured to be the multiplexed loworder address/data bus during accesses to external program and data memory. In this mode P0 has internal pullups.

Port 0 also receives the code bytes during Flash programming, and outputs the code bytes during program verification. External pullups are required during program verification.

### Port 1

Port 1 is an 8-bit bidirectional I/O port with internal pullups. The Port 1 output buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (I<sub>IL</sub>) because of the internal pullups.

Port 1 also receives the low-order address bytes during Flash programming and verification.

### Port 2

Port 2 is an 8-bit bidirectional I/O port with internal pullups. The Port 2 output buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current  $(I_{\rm IL})$  because of the internal pullups.

Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). In this application it uses strong internal pullups

when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.

Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.

### Port 3

Port 3 is an 8-bit bidirectional I/O port with internal pullups. The Port 3 output buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (I<sub>IL</sub>) because of the pullups.

Port 3 also serves the functions of various special features of the AT89C51 as listed below:

| Port Pin | Alternate Functions                    |  |  |  |

|----------|----------------------------------------|--|--|--|

| P3.0     | RXD (serial input port)                |  |  |  |

| P3.1     | TXD (serial output port)               |  |  |  |

| P3.2     | INTO (external interrupt 0)            |  |  |  |

| P3.3     | INT1 (external interrupt 1)            |  |  |  |

| P3.4     | T0 (timer 0 external input)            |  |  |  |

| P3.5     | T1 (timer 1 external input)            |  |  |  |

| P3.6     | WR (external data memory write strobe) |  |  |  |

| P3.7     | RD (external data memory read strobe)  |  |  |  |

Port 3 also receives some control signals for Flash programming and verification.

### RST

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device.

# ALE/PROG

Address Latch Enable output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.

In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.

If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.

# **PSEN**

Program Store Enable is the read strobe to external program memory.

When the AT89C51 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.

# EA/Vpp

External Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset.

$\overline{\mathsf{EA}}$  should be strapped to  $\mathsf{V}_{\mathsf{CC}}$  for internal program executions.

This pin also receives the 12-volt programming enable voltage ( $V_{PP}$ ) during Flash programming, for parts that require 12-volt  $V_{PP}$ .

### XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

### XTAL2

Output from the inverting oscillator amplifier.

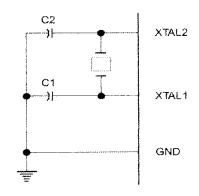

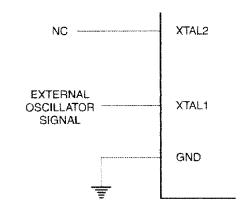

# **Oscillator Characteristics**

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

# Idle Mode

In idle mode, the CPU puts itself to sleep while all the onchip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset. It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

Figure 1. Oscillator Connections

Note: C1, C2 = 30 pF  $\pm$  10 pF for Crystals = 40 pF  $\pm$  10 pF for Ceramic Resonators

Figure 2. External Clock Drive Configuration

# Status of External Pins During Idle and Power Down Modes

| Mode       | Program Memory | ALE | PSEN | PORT0 | PORT1 | PORT2   | PORT3 |

|------------|----------------|-----|------|-------|-------|---------|-------|

| idle       | Internal       | 1   | 1    | Data  | Data  | Data    | Data  |

| Idle       | External       | 1   | 1    | Float | Data  | Address | Data  |

| Power Down | Internal       | 0   | 0    | Data  | Data  | Data    | Data  |

| Power Down | External       | 0   | 0    | Float | Data  | Data    | Data  |

AT89C51

# **Power Down Mode**

In the power down mode the oscillator is stopped, and the instruction that invokes power down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the power down mode is terminated. The only exit from power down is a hardware reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before  $V_{\rm CC}$  is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.

# **Program Memory Lock Bits**

On the chip are three lock bits which can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in the table below:

When lock bit 1 is programmed, the logic level at the  $\overline{EA}$  pin is sampled and latched during reset. If the device is powered up without a reset, the latch initializes to a random value, and holds that value until reset is activated. It is necessary that the latched value of  $\overline{EA}$  be in agreement with the current logic level at that pin in order for the device to function properly.

# Lock Bit Protection Modes

|   | Program Lock Bits |     | Б   | Protection Type                                                                                                                                                                                                        |

|---|-------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | LB1               | LB2 | LB3 |                                                                                                                                                                                                                        |

| 1 | U                 | U   | U   | No program lock features.                                                                                                                                                                                              |

| 2 | P                 | U   | U   | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset, and further programming of the Flash is disabled. |

| 3 | Р                 | P   | U   | Same as mode 2, also verify is disabled.                                                                                                                                                                               |

| 4 | P                 | Р   | Р   | Same as mode 3, also external execution is disabled.                                                                                                                                                                   |

# Programming the Flash

The AT89C51 is normally shipped with the on-chip Flash memory array in the erased state (that is, contents = FFH) and ready to be programmed. The programming interface accepts either a high-voltage (12-volt) or a low-voltage (V<sub>CC</sub>) program enable signal. The low voltage programming mode provides a convenient way to program the AT89C51 inside the user's system, while the high-voltage programming mode is compatible with conventional third party Flash or EPROM programmers.

The AT89C51 is shipped with either the high-voltage or low-voltage programming mode enabled. The respective top-side marking and device signature codes are listed in the following table.

|               | V <sub>PP</sub> = 12V | V <sub>PP</sub> = 5V |

|---------------|-----------------------|----------------------|

| Top-Side Mark | AT89C51               | AT89C51              |

|               | xxxx                  | xxxx-5               |

|               | yyww                  | yyww                 |

| Signature     | (030H)=1EH            | (030H)=1EH           |

|               | (031H)≂51H            | (031H)=51H           |

|               | (032H)=FFH            | (032H)=05H           |

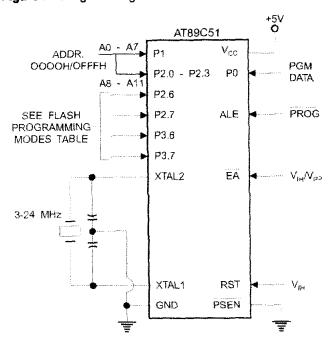

The AT89C51 code memory array is programmed byte-bybyte in either programming mode. To program any nonblank byte in the on-chip Flash Memory, the entire memory must be erased using the Chip Erase Mode. **Programming Algorithm:** Before programming the AT89C51, the address, data and control signals should be set up according to the Flash programming mode table and Figures 3 and 4. To program the AT89C51, take the following steps.

- Input the desired memory location on the address lines.

- 2. Input the appropriate data byte on the data lines.

- 3. Activate the correct combination of control signals.

- Raise EA/V<sub>PP</sub> to 12V for the high-voltage programming mode.

- Pulse ALE/PROG once to program a byte in the Flash array or the lock bits. The byte-write cycle is self-timed and typically takes no more than 1.5 ms. Repeat steps 1 through 5, changing the address and data for the entire array or until the end of the object file is reached.

Data Polling: The AT89C51 features Data Polling to indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written datum on PO.7. Once the write cycle has been completed, true data are valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.

**Ready/Busy:** The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.4 is pulled low after ALE goes high during programming to indicate BUSY. P3.4 is pulled high again when programming is done to indicate READY.

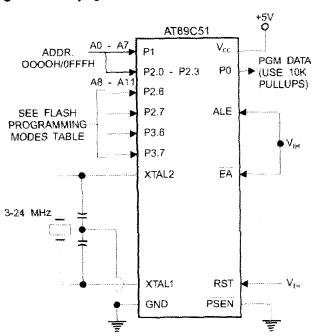

**Program Verify:** If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification. The lock bits cannot be verified directly. Verification of the lock bits is achieved by observing that their features are enabled.

Chip Erase: The entire Flash array is erased electrically by using the proper combination of control signals and by holding ALE/PROG low for 10 ms. The code array is written with all "1"s. The chip erase operation must be executed before the code memory can be re-programmed.

Reading the Signature Bytes: The signature bytes are read by the same procedure as a normal verification of locations 030H.

031H, and 032H, except that P3.6 and P3.7 must be pulled to a logic low. The values returned are as follows.

(030H) = 1EH indicates manufactured by Atmel

(031H) = 51H indicates 89C51

(032H) = FFH indicates 12V programming

(032H) = 05H indicates 5V programming

# **Programming Interface**

Every code byte in the Flash array can be written and the entire array can be erased by using the appropriate combination of control signals. The write operation cycle is self-timed and once initiated, will automatically time itself to completion.

All major programming vendors offer worldwide support for the Atmel microcontroller series. Please contact your local programming vendor for the appropriate software revision.

# Flash Programming Modes

| Mode Write Code Data |         | RST | PSEN | ALE/PROG | EA/V <sub>PP</sub> | P2.6 | P2.7 | P3.6 | P3.7 |

|----------------------|---------|-----|------|----------|--------------------|------|------|------|------|

|                      |         | Н   | H L  | H/12V    | -l/12V L           | Н    | Н    | Н    |      |

| Read Code Data       |         | Н   | L    | Н        | Н                  | L    | L    | Н    | Н    |

| Write Lock           | Bit - 1 | Н   | L    | ~~       | H/12V              | Н    | Н    | Н    | Н    |

|                      | Bit - 2 | Н   | L    |          | H/12V              | Н    | Н    | L    | L    |

|                      | Bit - 3 | Н   | L    |          | H/12V              | Н    | L    | H    | L    |

| Chip Erase           |         | Н   | L    | (1)      | H/12V              | Н    | L    | L    | L    |

| Read Signature B     | 3yte    | Н   | L    | н        | Н                  | L.   | L    | L    | L    |

Note: 1. Chip Erase requires a 10-ms PROG pulse.

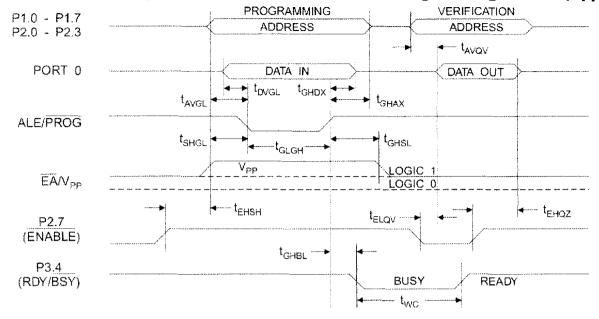

Figure 3. Programming the Flash

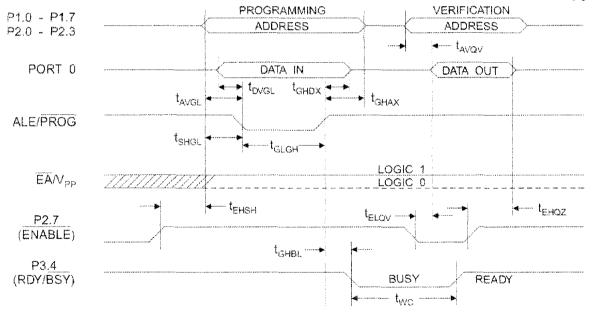

Figure 4. Verifying the Flash

# Flash Programming and Verification Characteristics

$T_A = 0$ °C to 70°C,  $V_{CC} = 5.0 \pm 10\%$

| Symbol                         | Parameter                             | Min                 | Max                 | Units |

|--------------------------------|---------------------------------------|---------------------|---------------------|-------|

| V <sub>PP</sub> <sup>(1)</sup> | Programming Enable Voltage            | 11.5                | 12.5                | V     |

| lpp <sup>(1)</sup>             | Programming Enable Current            |                     | 1.0                 | mA    |

| 1/t <sub>CLCL</sub>            | Oscillator Frequency                  | 3                   | 24                  | MHz   |

| t <sub>AVGL</sub>              | Address Setup to PROG Low             | 48t <sub>CLCL</sub> |                     |       |

| t <sub>GHAX</sub>              | Address Hold After PROG               | 48t <sub>CLCL</sub> |                     |       |

| t <sub>DVGL</sub>              | Data Setup to PROG Low                | 48t <sub>CLCL</sub> |                     |       |

| t <sub>GHDX</sub>              | Data Hold After PROG                  | 48t <sub>CLCL</sub> |                     |       |

| t <sub>EHSH</sub>              | P2.7 (ENABLE) High to V <sub>PP</sub> | 48t <sub>CLCL</sub> |                     |       |

| t <sub>SHGL</sub>              | V <sub>PP</sub> Setup to PROG Low     | 10                  |                     | μs    |

| t <sub>GHSL</sub> (1)          | V <sub>PP</sub> Hold After PROG       | 10                  |                     | μs    |

| t <sub>GLGH</sub>              | PROG Width                            | 1                   | 110                 | μs    |

| t <sub>AVQV</sub>              | Address to Data Valid                 |                     | 48t <sub>CLCL</sub> |       |

| t <sub>ELQV</sub>              | ENABLE Low to Data Valid              |                     | 48t <sub>CLCL</sub> |       |

| t <sub>EHQZ</sub>              | Data Float After ENABLE               | 0                   | 48t <sub>CLCL</sub> |       |

| t <sub>GHBL</sub>              | PROG High to BUSY Low                 |                     | 1.0                 | μs    |

| t <sub>WC</sub>                | Byte Write Cycle Time                 |                     | 2.0                 | ms    |

Note: 1. Only used in 12-volt programming mode.

# Flash Programming and Verification Waveforms - High Voltage Mode (V<sub>PP</sub> = 12V)

# Flash Programming and Verification Waveforms - Low Voltage Mode ( $V_{PP} = 5V$ )

# **Absolute Maximum Ratings\***

| Operating Temperature                        | 55°C to +125°C  |

|----------------------------------------------|-----------------|

| Storage Temperature                          | -65°C to +150°C |

| Voltage on Any Pin<br>with Respect to Ground | 1.0V to +7.0V   |

| Maximum Operating Voltage                    | 6.6V            |

| DC Output Current                            | 15.0 mA         |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **DC Characteristics**

$T_A$  = -40°C to 85°C,  $V_{CC}$  = 5.0V ± 20% (unless otherwise noted)

| Symbol           | Parameter                                                | Condition                                        | Min                       | Max                       | Units |

|------------------|----------------------------------------------------------|--------------------------------------------------|---------------------------|---------------------------|-------|

| V <sub>IL</sub>  | Input Low Voltage                                        | (Except EA)                                      | -0.5                      | 0.2 V <sub>CC</sub> - 0.1 | V     |

| V <sub>IL1</sub> | Input Low Voltage (EA)                                   |                                                  | -0.5                      | 0.2 V <sub>CC</sub> - 0.3 | V     |

| V <sub>IH</sub>  | Input High Voltage                                       | (Except XTAL1, RST)                              | 0.2 V <sub>CC</sub> + 0.9 | V <sub>CC</sub> + 0.5     | ٧     |

| V <sub>IH1</sub> | Input High Voltage                                       | (XTAL1, RST)                                     | 0.7 V <sub>CC</sub>       | V <sub>CC</sub> + 0.5     | ٧     |

| v <sub>ol</sub>  | Output Low Voltage <sup>(1)</sup> (Ports 1,2,3)          | I <sub>OL</sub> = 1.6 mA                         |                           | 0.45                      | ٧     |

| V <sub>OL1</sub> | Output Low Voltage <sup>(1)</sup><br>(Port 0, ALE, PSEN) | I <sub>OL</sub> = 3.2 mA                         |                           | 0.45                      | ٧     |

| V <sub>OH</sub>  | Output High Voltage                                      | $I_{OH}$ = -60 $\mu$ A, $V_{CC}$ = 5V $\pm$ 10%  | 2.4                       |                           | V     |

|                  | (Ports 1,2,3, ALE, PSEN)                                 | I <sub>OH</sub> = -25 μA                         | 0.75 V <sub>CC</sub>      |                           | V     |

|                  |                                                          | I <sub>OH</sub> = -10 μA                         | 0.9 V <sub>CC</sub>       |                           | V     |

| V <sub>OH1</sub> | Output High Voltage                                      | $I_{OH}$ = -800 $\mu$ A, $V_{CC}$ = 5V $\pm$ 10% | 2.4                       |                           | ٧     |

|                  | (Port 0 in External Bus Mode)                            | I <sub>OH</sub> = -300 μA                        | 0.75 V <sub>CC</sub>      |                           | ٧     |

|                  |                                                          | I <sub>OH</sub> = ~80 μA                         | 0.9 V <sub>CC</sub>       |                           | V     |

| I <sub>IL</sub>  | Logical 0 Input Current (Ports 1,2,3)                    | V <sub>IN</sub> = 0.45V                          |                           | -50                       | μА    |

| I <sub>TL</sub>  | Logical 1 to 0 Transition Current (Ports 1,2,3)          | $V_{IN} = 2V$ , VCC = 5V ± 10%                   |                           | -650                      | μА    |

| ILI              | Input Leakage Current (Port 0, EA)                       | 0.45 < V <sub>IN</sub> < V <sub>CC</sub>         |                           | ±10                       | μА    |

| RRST             | Reset Pulldown Resistor                                  |                                                  | 50                        | 300                       | ΚΩ    |

| C <sub>IO</sub>  | Pin Capacitance                                          | Test Freq. = 1 MHz, T <sub>A</sub> = 25°C        |                           | 10                        | pF    |

| icc              | Power Supply Current                                     | Active Mode, 12 MHz                              |                           | 20                        | mA    |

|                  |                                                          | idle Mode, 12 MHz                                |                           | 5                         | mA    |

|                  | Power Down Mode <sup>(2)</sup>                           | V <sub>CC</sub> = 6V                             |                           | 100                       | μА    |

|                  |                                                          | V <sub>CC</sub> = 3V                             |                           | 40                        | μА    |

Notes: 1. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum IOL per port pin: 10 mA

Maximum IOL per 8-bit port: Port 0: 26 mA

Ports 1, 2, 3: 15 mA

Maximum total I<sub>OL</sub> for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

2. Minimum V<sub>CC</sub> for Power Down is 2V.

# **AC Characteristics**

(Under Operating Conditions; Load Capacitance for Port 0, ALE/PROG, and PSEN = 100 pF; Load Capacitance for all other outputs = 80 pF)

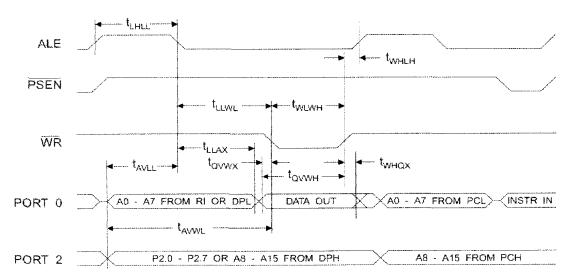

# **External Program and Data Memory Characteristics**

| Symbol              | Parameter                          | 12 MHz ( | Oscillator | 16 to 24 Mi             | Iz Oscillator           | Units |

|---------------------|------------------------------------|----------|------------|-------------------------|-------------------------|-------|

|                     |                                    | Min      | Max        | Min                     | Max                     |       |

| 1/t <sub>CLCL</sub> | Oscillator Frequency               |          |            | 0                       | 24                      | MHz   |

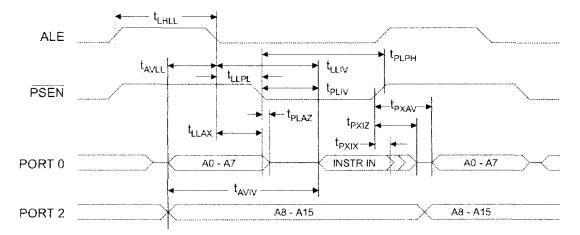

| t <sub>LHLL</sub>   | ALE Pulse Width                    | 127      |            | 2t <sub>CLCL</sub> -40  |                         | ns    |

| t <sub>AVLL</sub>   | Address Valid to ALE Low           | 43       |            | t <sub>CLCL</sub> -13   |                         | ns    |

| t <sub>LLAX</sub>   | Address Hold After ALE Low         | 48       |            | t <sub>CLCL</sub> -20   |                         | ns    |

| t <sub>LLIV</sub>   | ALE Low to Valid Instruction In    |          | 233        |                         | 4t <sub>CLCL</sub> -65  | ns    |

| t <sub>LLPL</sub>   | ALE Low to PSEN Low                | 43       |            | t <sub>CLCL</sub> -13   |                         | ns    |

| t <sub>PLPH</sub>   | PSEN Pulse Width                   | 205      |            | 3t <sub>CLCL</sub> -20  |                         | ns    |

| t <sub>PUV</sub>    | PSEN Low to Valid Instruction In   |          | 145        |                         | 3t <sub>CLCL</sub> -45  | ns    |

| t <sub>PXIX</sub>   | Input Instruction Hold After PSEN  | 0        |            | 0                       |                         | ns    |

| t <sub>PXIZ</sub>   | Input Instruction Float After PSEN |          | 59         |                         | t <sub>CLCL</sub> -10   | ns    |

| t <sub>PXAV</sub>   | PSEN to Address Valid              | 75       |            | t <sub>CLCL</sub> -8    |                         | ns    |

| t <sub>AVIV</sub>   | Address to Valid Instruction In    |          | 312        |                         | 5t <sub>CLCL</sub> -55  | ns    |

| t <sub>PLAZ</sub>   | PSEN Low to Address Float          |          | 10         |                         | 10                      | ns    |

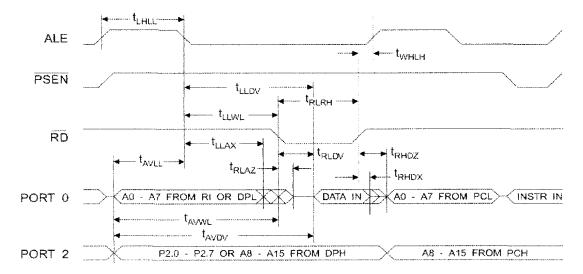

| t <sub>RLRH</sub>   | RD Pulse Width                     | 400      |            | 6t <sub>CLCL</sub> -100 |                         | ns    |

| t <sub>WLWH</sub>   | WR Pulse Width                     | 400      |            | 6t <sub>CLCL</sub> -100 |                         | ns    |

| t <sub>RLDV</sub>   | RD Low to Valid Data In            |          | 252        |                         | 5t <sub>CLCL</sub> -90  | ns    |

| t <sub>RHDX</sub>   | Data Hold After RD                 | 0        |            | 0                       |                         | ns    |

| t <sub>RHDZ</sub>   | Data Float After RD                |          | 97         |                         | 2t <sub>CLCL</sub> -28  | ns    |

| t <sub>LLDV</sub>   | ALE Low to Valid Data In           |          | 517        |                         | 8t <sub>CLCL</sub> -150 | ns    |

| t <sub>AVDV</sub>   | Address to Valid Data In           |          | 585        |                         | 9t <sub>CLCL</sub> -165 | ns    |

| t <sub>LLWL</sub>   | ALE Low to RD or WR Low            | 200      | 300        | 3t <sub>CLCL</sub> -50  | 3t <sub>CLCL</sub> +50  | ns    |

| t <sub>AVWL</sub>   | Address to RD or WR Low            | 203      |            | 4t <sub>CLCL</sub> -75  |                         | ns    |

| t <sub>QVWX</sub>   | Data Valid to WR Transition        | 23       |            | t <sub>CLCL</sub> -20   |                         | ns    |

| t <sub>QVWH</sub>   | Data Valid to WR High              | 433      |            | 7t <sub>CLCL</sub> -120 |                         | ns    |

| twhax               | Data Hold After WR                 | 33       |            | t <sub>CLCL</sub> -20   |                         | ns    |

| t <sub>RLAZ</sub>   | RD Low to Address Float            |          | 0          |                         | 0                       | ns    |

| twhLH               | RD or WR High to ALE High          | 43       | 123        | t <sub>CLCL</sub> -20   | t <sub>CLCL</sub> +25   | ns    |

# **External Program Memory Read Cycle**

# **External Data Memory Read Cycle**

# **External Data Memory Write Cycle**

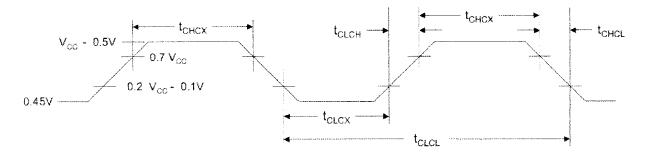

# **External Clock Drive Waveforms**

# **External Clock Drive**

| Symbol              | Parameter            | Min  | Max | Units |

|---------------------|----------------------|------|-----|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0    | 24  | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 41.6 |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 15   |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 15   |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |      | 20  | ns    |

| t <sub>CHCL</sub>   | Fall Time            |      | 20  | ns    |

AT89C51

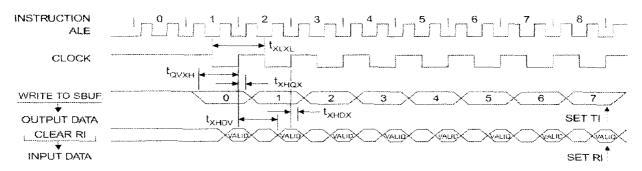

# **Serial Port Timing: Shift Register Mode Test Conditions**

$(V_{CC} = 5.0 \text{ V} \pm 20\%; \text{ Load Capacitance} = 80 \text{ pF})$

| Symbol            | Parameter                                | 12 Mi | iz Osc | Variable                 | Oscillator               | Units |

|-------------------|------------------------------------------|-------|--------|--------------------------|--------------------------|-------|

|                   |                                          | Min   | Max    | Min                      | Max                      |       |

| t <sub>XLXL</sub> | Serial Port Clock Cycle Time             | 1.0   |        | 12t <sub>CLCL</sub>      |                          | μs    |

| t <sub>QVXH</sub> | Output Data Setup to Clock Rising Edge   | 700   |        | 10t <sub>CLCL</sub> -133 |                          | ns    |

| t <sub>XHQX</sub> | Output Data Hold After Clock Rising Edge | 50    |        | 2t <sub>CLCL</sub> -117  |                          | ns    |

| t <sub>XHDX</sub> | Input Data Hold After Clock Rising Edge  | 0     |        | 0                        |                          | ns    |

| t <sub>XHDV</sub> | Clock Rising Edge to Input Data Valid    | "     | 700    |                          | 10t <sub>CLCL</sub> -133 | ns    |

# **Shift Register Mode Timing Waveforms**

Note:

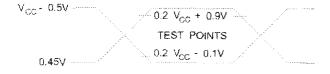

# AC Testing Input/Output Waveforms<sup>(1)</sup>

# Float Waveforms<sup>(1)</sup>

Note: 1. AC Inputs during testing are driven at V<sub>CC</sub> - 0.5V for a logic 1 and 0.45V for a logic 0. Timing measurements are made at V<sub>IH</sub> min. for a logic 1 and V<sub>IL</sub>

max. for a logic 0.

For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs. A port pin begins to float when 100 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs.

# Ordering Information

| Speed<br>(MHz) | Power<br>Supply | Ordering Code | Package       | Operation Range  |

|----------------|-----------------|---------------|---------------|------------------|

| 12             | 5V ± 20%        | AT89C51-12AC  | 44A           | Commercial       |

|                |                 | AT89C51-12JC  | 44J           | (0°C to 70°C)    |

|                |                 | AT89C51-12PC  | 40P6          |                  |

|                |                 | AT89C51-12QC  | 44Q           |                  |

|                |                 | AT89C51-12Al  | 44A           | Industrial       |

|                |                 | AT89C51-12JI  | 44.j          | (-40°C to 85°C)  |

|                |                 | AT89C51-12PI  | 40P6          |                  |

|                |                 | AT89C51-12QI  | 44Q           |                  |

|                |                 | AT89C51-12AA  | 44A           | Automotive       |

|                |                 | AT89C51-12JA  | 44.J          | (-40°C to 105°C) |

|                |                 | AT89C51-12PA  | 40P6          |                  |

|                |                 | AT89C51-12QA  | 44Q           |                  |

| 16             | 5V ± 20%        | AT89C51-16AC  | 44A           | Commercial       |

|                |                 | AT89C51-16JC  | 44J           | (0°C to 70°C)    |

|                |                 | AT89C51-16PC  | 40 <b>P</b> 6 |                  |

|                |                 | AT89C51-16QC  | 44Q           |                  |

|                |                 | AT89C51-16AI  | 44A           | Industrial       |

|                |                 | AT89C51-16JI  | 44J           | (-40°C to 85°C)  |

|                |                 | AT89C51-16PI  | 40P6          |                  |

|                |                 | AT89C51-16QI  | 44Q           |                  |

|                |                 | AT89C51-16AA  | 44A           | Automotive       |

|                |                 | AT89C51-16JA  | 44J           | (-40°C to 105°C) |

|                |                 | AT89C51-16PA  | 40P6          |                  |

|                |                 | AT89C51-16QA  | 44Q           |                  |

| 20             | 5V ± 20%        | AT89C51-20AC  | 44A           | Commercial       |

|                |                 | AT89C51-20JC  | 44J           | (0°C to 70°C)    |

|                |                 | AT89C51-20PC  | 40P6          |                  |

|                |                 | AT89C51-20QC  | 44Q           |                  |

|                |                 | AT89C51-20AI  | 44A           | Industrial       |

|                |                 | AT89C51-20JI  | 44.J          | (-40°C to 85°C)  |

|                |                 | AT89C51-20PI  | 40P6          |                  |

|                |                 | AT89C51-20QI  | 44Q           |                  |

# Ordering Information

| Speed<br>(MHz) | Power<br>Supply | Ordering Code | Package | Operation Range |

|----------------|-----------------|---------------|---------|-----------------|

| 24             | 5V ± 20%        | AT89C51-24AC  | 44A     | Commercial      |

|                |                 | AT89C51-24JC  | 44J     | (0°C to 70°C)   |

|                |                 | AT89C51-24PC  | 44P6    |                 |

|                |                 | AT89C51-24QC  | 44Q     |                 |

|                | İ               | AT89C51-24AI  | 44A     | Industrial      |

|                |                 | AT89C51-24JI  | 44J     | (-40°C to 85°C) |

|                |                 | AT89C51-24PI  | 44P6    |                 |

|                |                 | AT89C51-24QI  | 44Q     |                 |

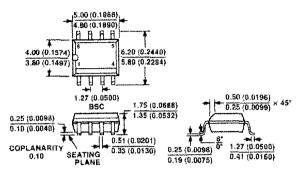

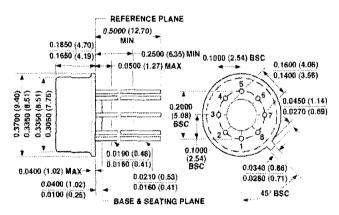

|      | Package Type                                             |

|------|----------------------------------------------------------|

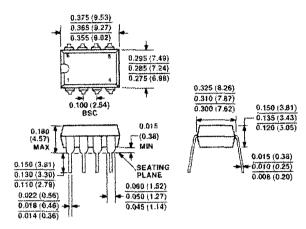

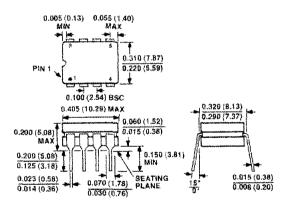

| 44A  | 44 Lead, Thin Plastic Gull Wing Quad Flatpack (TQFP)     |

| 44J  | 44 Lead, Plastic J-Leaded Chip Carrier (PLCC)            |

| 40P6 | 40 Lead, 0.600" Wide, Plastic Dual Inline Package (PDIP) |

| 44Q  | 44 Lead, Plastic Gull Wing Quad Flatpack (PQFP)          |

# 19-0381; Rev 2: 9/01 EVALUATION KIT MANUAL AVAILABLE

# MIXIM

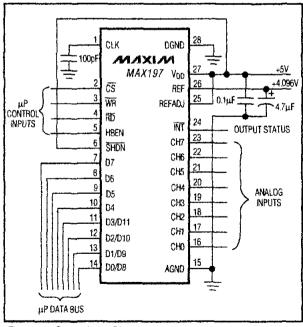

# Multi-Range ( $\pm 10V$ , $\pm 5V$ , + 10V, + 5V), Single +5V, 12-Bit DAS with 8+4 Bus Interface

# **General Description**

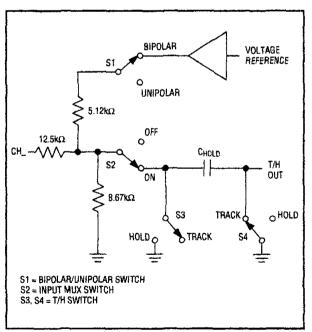

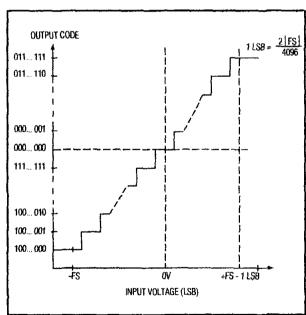

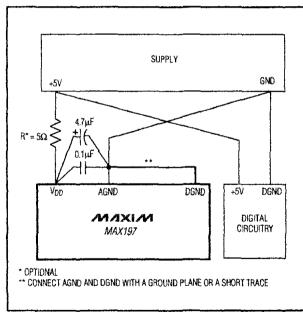

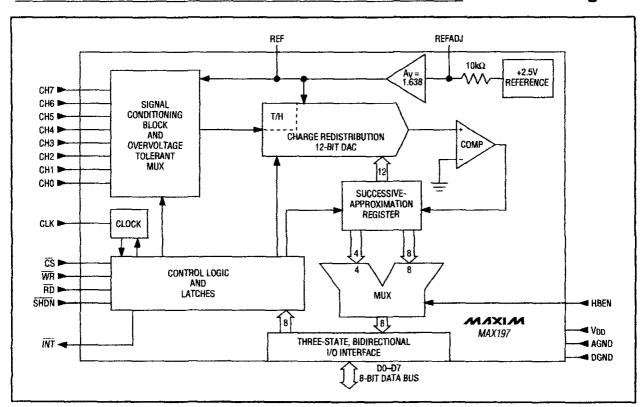

The MAX197 multi-range, 12-bit data-acquisition system (DAS) requires only a single +5V supply for operation, yet accepts signals at its analog inputs that may soan both above the power-supply rail and below ground. This system provides 8 analog input channels that are independently software programmable for a variety of ranges:  $\pm 10V$ ,  $\pm 5V$ , 0V to +10V, or 0V to +5V. This increases effective dynamic range to 14 bits, and provides the user flexibility to interface 4mA-to-20mA, ±12V, and ±15V powered sensors to a single +5V system. In addition, the converter is overvoltage tolerant to ±16.5V; a fault condition on any channel does not affect the conversion result of the selected channel. Other features include a 5MHz bandwidth track/hold, a 100ksps throughput rate, software-selectable internal or external clock and acquisition, 8+4 parallel interface, and an internal 4.096V or an external reference.

A hardware SHDN pin and two programmable powerdown modes (STBYPD, FULLPD) are provided for lowcurrent shutdown between conversions. In STBYPD mode, the reference buffer remains active, eliminating start-up delays

The MAX197 employs a standard microprocessor (µP) interface. A three-state data I/O port is configured to operate with 8-bit data buses, and data-access and bus-release timing specifications are compatible with most popular µPs. All logic inputs and outputs are TTL/CMOS compatible.

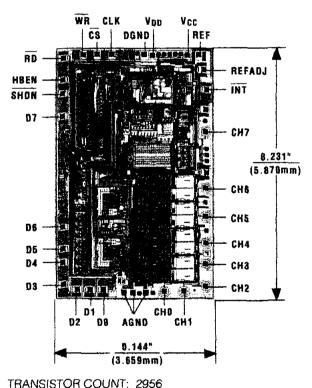

The MAX197 is available in 28-pin DIP, wide SO, SSOP, and ceramic SB packages.

For a different combination of ranges (±4V, ±2V, 0V to 4V, 0V to 2V), refer to the MAX199 data sheet. For 12-bit bus interface, refer to the MAX196 and MAX198 data

# **Applications**

Industrial-Control Systems **Bobotics** Data-Acquisition Systems Automatic Testing Systems Medical Instruments Telecommunications

Functional Diagram appears at end of data sheet.

### Features

- 12-Bit Resolution, 1/2LSB Linearity

- Single +5V Operation

- Software-Selectable Input Ranges: ±10V, ±5V, 0V to 10V, 0V to 5V

- Fault-Protected Input Multiplexer (±16.5V)

- 8 Analog Input Channels

- ♦ 6µs Conversion Time, 100ksps Sampling Rate

- Internal or External Acquisition Control

- Internal 4.096V or External Reference

- Two Power-Down Modes

- Internal or External Clock

# **Ordering Information**

|            |              | —                     |

|------------|--------------|-----------------------|

| PART       | TEMP RANGE   | PIN-PACKAGE           |

| MAX197ACNI | 0°C to +70°C | 28 Narrow Plastic DIP |

| MAX197BCNI | 0°C to +70°C | 28 Narrow Plastic DIP |

| MAX197ACWI | 0°C to +70°C | 28 Wide SO            |

| MAX197BCWI | 0°C to +70°C | 28 Wide SO            |

| MAX197ACAI | 0°C to +70°C | 28 SSOP               |

| MAX197BCAI | 0°C to +70°C | 28 SSOP               |

| MAX197BC/D | 0°C to +70°C | Dice*                 |

|            |              |                       |

Ordering Information continued at end of data sheet. \*Dice are specified at  $T_A = +25$ °C, DC parameters only.

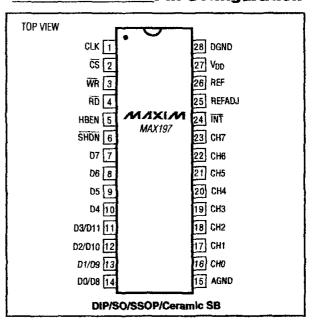

# Pin Configuration

MIXLM

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# Multi-Range (±10V, ±5V, +10V, +5V), Single +5V, 12-Bit DAS with 8+4 Bus Interface

# **ABSOLUTE MAXIMUM RATINGS**

| VDD to AGND                        | 0.3V to +7V                      |

|------------------------------------|----------------------------------|

| AGND to DGND                       |                                  |

| REF to AGND                        | 0.3V to (V <sub>DD</sub> + 0.3V) |

| REFADJ to AGND                     |                                  |

| Digital Inputs to DGND             | 0.3V to (V <sub>DD</sub> + 0.3V) |

| Digital Outputs to DGND            |                                  |

| CH0-CH7 to AGND                    |                                  |

| Continuous Power Dissipation (TA = | : +70°C)                         |

| Narrow Plastic DIP (derate 14.29mW | /°C above +70°C)1143mW           |

| Wide SO (derate 12.50mW/°C abo     | ve +70°C)1000mW                  |

| SSOP (derate 9.52mW/°C above +     | 70°C)762mW                       |

| Narrow Ceramic SB (derate 20.00m)  |                                  |

| Operating Temperature Ranges      |                |

|-----------------------------------|----------------|

| MAX197_C                          | 0°C to +70°C   |

| MAX197_E                          |                |

| MAX197_M                          | 55°C to +125°C |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 5V \pm 5\%; unipolar/bipolar range; external reference mode, V_{REF} = 4.096V; 4.7\mu F at REF pin; external clock, fCLK = 2.0MHz with 50% duty cycle; TA = TMIN to TMAX, unless otherwise noted.)$

| PARAMETER                          | SYMBOL      | CONDITIONS                                              |                                       | MIN          | TYP         | MAX  | UNITS     |  |

|------------------------------------|-------------|---------------------------------------------------------|---------------------------------------|--------------|-------------|------|-----------|--|

| ACCURACY (Note 1)                  |             | 111                                                     | · · · · · · · · · · · · · · · · · · · | <del> </del> | ****        |      |           |  |

| Resolution                         |             |                                                         |                                       | 12           |             |      | Bits      |  |

| Integral Nonlinearity              | INL         | MAX197A                                                 |                                       |              | <del></del> | ±1/2 | LCD       |  |

| megrai Nonimearity                 | HAL         | MAX197B                                                 |                                       |              |             | ±1   | LSB       |  |

| Differential Nonlinearity          | DNL         |                                                         |                                       |              |             | ±1   | LSB       |  |

|                                    |             | Unipolar                                                | MAX197A                               |              |             | ±3   |           |  |

| Offset Error                       |             | l                                                       | MAX197B                               |              |             | ±5   | LSB       |  |

| Oliset Elloi                       |             | Bipolar                                                 | MAX197A                               |              |             | ±5   | LOD       |  |

|                                    |             | ырыаг                                                   | MAX197B                               |              |             | ±10  | 1         |  |

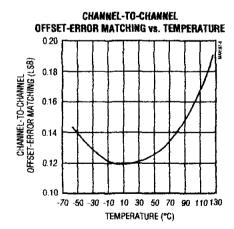

| Channel-to-Channel Offset          |             | Unipolar                                                |                                       |              | ±0.1        |      | LSB       |  |

| Error Matching                     |             | Bipolar                                                 |                                       |              | ±0.5        |      | LOD       |  |

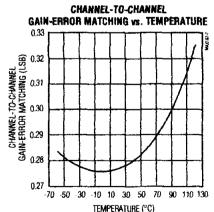

| Gain Error                         |             | Unipolar                                                | MAX197A                               |              |             | ±7   | LSB       |  |

|                                    |             | Origodiar                                               | MAX197B                               |              |             | ±10  |           |  |

| (Note 2)                           |             | Bipolar                                                 | MAX197A                               |              |             | ±7   |           |  |

|                                    |             | MAX197B                                                 |                                       |              |             | ±10  | 1         |  |

| Gain Temperature Coefficient       |             | Unipolar                                                |                                       |              | 3           |      | ppm/°C    |  |

| (Note 2)                           |             | Bipolar                                                 |                                       | 5            |             |      | - ppin/-C |  |

| DYNAMIC SPECIFICATIONS (1          | OkHz sine-w | ave input, ±10Vp-p, t                                   | SAMPLE = 100ksps)                     |              |             |      | A         |  |

| Signal-to-Noise + Distortion Ratio | SINAD       |                                                         | MAX197A                               | 70           |             |      | dB        |  |

| Signal-to-Noise + Distortion hatto | SINAU       |                                                         | MAX197B                               | 69           |             |      | d ub      |  |

| Total Harmonic Distortion          | THD         | Up to the 5th harmonic                                  |                                       |              | -85         | -78  | ₫B        |  |

| Spurious-Free Dynamic Range        | SFDR        |                                                         |                                       | 80           |             |      | d₿        |  |

| Channel-to-Channel Crosstalk       |             | 50kHz, V <sub>IN</sub> = ±5V (Note 3)                   |                                       |              | -86         |      | dB        |  |

| Aperture Delay                     |             | External CLK mode/external acquisition control          |                                       |              | 15          |      | ns        |  |

| Aperture Jitter                    |             | External CLK mode control                               | external acquisition                  |              | <50         |      | ps        |  |

| Aportaro viller                    |             | Internal CLK mode/internal acquisition control (Note 4) |                                       |              | 10          |      | ns        |  |

# Multi-Range (±10V, ±5V, +10V, +5V), Single +5V, 12-Bit DAS with 8+4 Bus Interface

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 5\%; unipolar/bipolar range; external reference mode, V_{REF} = 4.096V; 4.7\muF$  at REF pin; external clock, f<sub>CLK</sub> = 2.0MHz with 50% duty cycle; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                           | SYMBOL          | CONE                     | ITIONS                                 | MIN      | TYP    | MAX   | UNITS       |  |

|-------------------------------------|-----------------|--------------------------|----------------------------------------|----------|--------|-------|-------------|--|

| ANALOG INPUT                        | <u> </u>        | <del></del>              | ······································ |          | ····   |       | <del></del> |  |

| Track/Hold Acquisition Time         |                 | fCLK = 2.0MHz            |                                        |          |        | 3     | μs          |  |

|                                     |                 |                          | ±10V range                             | <b>†</b> | 5      | ***** |             |  |

| 0                                   |                 | 0.00 # 17                | ±5V range                              | 1        | 2.5    |       |             |  |

| Small-Signal Bandwidth              |                 | -3dB rolloff             | OV to 10V range                        | 1        | 2.5    |       | MHz         |  |

|                                     |                 |                          | 0V to 5V range                         |          | 1.25   |       |             |  |

|                                     |                 | Unicolor                 | <del></del>                            | 0        |        | 10    |             |  |

| Input Voltage Range                 |                 | Unipolar                 |                                        | 0        |        | 5     | V           |  |

| (See Table 1)                       |                 | Disales                  |                                        | -10      |        | 10    | 1 °         |  |

|                                     |                 | Bipolar                  |                                        | -5       |        | 5     |             |  |

| Input Current                       |                 | I le ie ele e            | 0V to 10V range                        |          |        | 720   |             |  |

|                                     |                 | Unipolar                 | 0V to 5V range                         |          |        | 360   |             |  |

|                                     |                 | Singler                  | -10V to 10V range                      | -1200    |        | 720   | - µA        |  |

|                                     |                 | Bipolar                  | -5V to 5V range                        | -600     |        | 360   |             |  |

| Innut Dunamia Basistanaa            |                 | Unipolar                 |                                        |          | 21     |       | kΩ          |  |

| Input Dynamic Resistance            |                 | Bipolar                  |                                        |          | 16     |       | K12         |  |

| Input Capacitance                   |                 | (Note 5)                 |                                        |          |        | 40    | pF          |  |

| INTERNAL REFERENCE                  |                 |                          |                                        |          |        |       |             |  |

| REF Output Voltage                  | VREF            | T <sub>A</sub> = +25°C   |                                        | 4.076    | 4.096  | 4.116 | V           |  |

| REF Output Tempco                   | TC VREF         |                          |                                        |          | 40     |       | ppm/°C      |  |

| Output Short-Circuit Current        |                 |                          |                                        |          |        | 30    | mA          |  |

| Load Regulation                     |                 | 0mA to 0.5mA output of   | current (Note 6)                       |          |        | 7.5   | mV          |  |

| Capacitive Bypass at REF            |                 |                          |                                        | 4.7      |        |       | μF          |  |

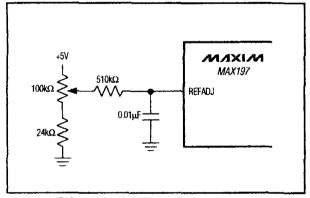

| REFADJ Output Voltage               |                 |                          |                                        | 2.465    | 2.500  | 2.535 | V           |  |

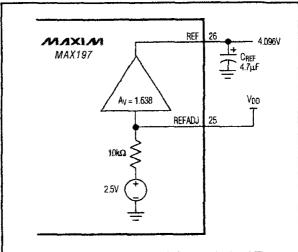

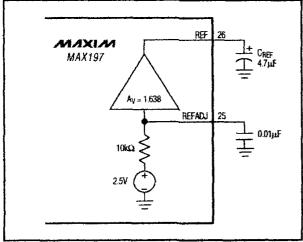

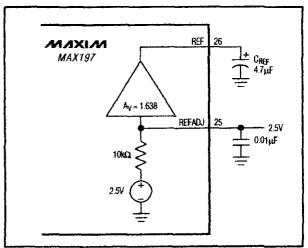

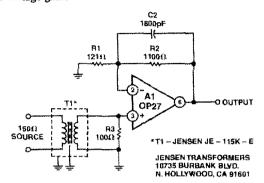

| REFADJ Adjustment Range             |                 | With recommended cir     | cuit (Figure 1)                        |          | ±1.5   |       | %           |  |

| Buffer Voltage Gain                 |                 |                          |                                        |          | 1.6384 |       | V/V         |  |

| REFERENCE INPUT (Buffer d           | isabled, refere | ence input applied to RE | F pin)                                 |          |        |       |             |  |

| Input Voltage Range                 |                 |                          |                                        | 2.4      |        | 4.18  | V           |  |

| Input Current                       |                 | VREF = 4.18V             | Normal or STANDBY power-down mode      |          |        | 400   | μΑ          |  |

| mpar ourrent                        |                 | VHEF = 4, 104            | FULL power-down mode                   |          |        | 1     | μΑ          |  |

| Input Resistance                    |                 | Normal or STANDBY p      |                                        | 10       |        |       | kΩ          |  |

| inhar ucolorance                    |                 | FULL power-down mo       | de                                     | 5        |        |       | MΩ          |  |

| REFADJ Threshold for Buffer Disable |                 |                          |                                        |          | mV     |       | ٧           |  |

| 44 | 4 | V | ı | 44 |

|----|---|---|---|----|

|    | _ | - | я |    |

# Multi-Range (±10V, ±5V, +10V, +5V), Single +5V, 12-Bit DAS with 8+4 Bus Interface

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 5\%; unipolar/bipolar range; external reference mode, V_{REF} = 4.096V; 4.7\mu F at REF pin; external clock, fCLK = 2.0MHz with 50% duty cycle; TA = TMIN to TMAX, unless otherwise noted.)$

| PARAMETER                          | SYMBOL       | CONDITIONS                              |                   | MIN     | TYP         | MAX    | UNITS |  |

|------------------------------------|--------------|-----------------------------------------|-------------------|---------|-------------|--------|-------|--|

| POWER REQUIREMENTS                 | L            | <u> </u>                                |                   |         | <del></del> | ······ | L     |  |

| Supply Voltage                     | VDD          |                                         |                   | 4.75    |             | 5.25   | ٧     |  |

|                                    |              | Normal mode, bipolar                    | ranges            |         |             | 18     |       |  |

| Curanti Current                    |              | Normal mode, unipolar                   | ranges            | 1       | 6           | 10     | mA    |  |

| Supply Current                     | 100          | Standby power-down (                    | STBYPD)           |         | 700         | 850    |       |  |

|                                    |              | Full power-down mode                    | (FULLPD) (Note 7) |         |             | 120    | μA    |  |

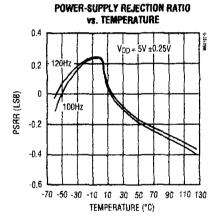

| Power-Supply Rejection Ratio       | PSRR         | External reference = 4.                 | 096V              |         |             | ±1/2   | LSB   |  |

| (Note 8)                           | ronn         | Internal reference                      |                   |         | ±1/2        |        | LOD   |  |

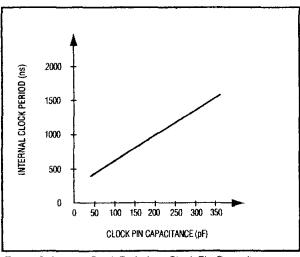

| TIMING                             | <del> </del> | <u> </u>                                |                   |         |             |        |       |  |

| Internal Clock Frequency           | fCLK         | CCLK = 100pF                            |                   | 1.25    | 1.56        | 2.00   | MHz   |  |

| External Clock Frequency Range     | fCLK         |                                         |                   | 0.1     |             | 2.0    | MHz   |  |

|                                    | t4001        | Internal conviction                     | External CLK      | 3.0     |             |        | μs    |  |

| Acquisition Time                   | tacqi        | Internal acquisition                    | Internal CLK      | 3.0     |             | 5.0    |       |  |

|                                    | tions        | External acquisition (Note 9)           |                   | 3.0     |             |        | μο    |  |

|                                    | TACGE        | After FULLPD or STBYPD                  |                   |         | 5           |        |       |  |

| Conversion Time                    | toonu        | External CLK                            |                   | 6.0     |             |        | us    |  |

| Conversion Time                    | tCONV        | Internal CLK, CCLK = 1                  | 00pF              | 6.0     | 7.7         | 10.0   | jus ! |  |

| Throughput Rate                    |              | External CLK                            |                   |         |             | 100    | ksps  |  |

| mroughput Nate                     |              | Internal CLK, CCLK = 1                  | 00pF              | 62      |             |        | ksps  |  |

| Bandgap Reference<br>Start-Up Time |              | Power-up (Note 10)                      |                   |         | 200         |        | μs    |  |

| Defended B. Was Cattley            |              | To 0.1mV REF bypass                     | CREF = 4.7µF      |         | 8           |        |       |  |

| Reference Buffer Settling          |              | capacitor fully discharged              | CREF = 33µF       |         | 60          |        | ms    |  |

| DIGITAL INPUTS (D7-D0, CLK,        | RD, WR, CS   | , HBEN, SHDN) (Note 1                   | 1)                |         |             |        |       |  |

| Input High Voltage                 | VINH         |                                         |                   | 2.4     |             |        | V     |  |

| Input Low Voltage                  | VINL         |                                         |                   |         |             | 8.0    | V     |  |

| Input Leakage Current              | IN           | V <sub>IN</sub> = 0V or V <sub>DD</sub> |                   |         |             | ±10    | μА    |  |

| Input Capacitance                  | CiN          | (Note 5)                                |                   |         |             | 15     | pF    |  |

| DIGITAL OUTPUTS (D7-D4, D3         | /D11, D2/D1  | 10, D1/D9, D0/D8, ĪNT)                  |                   |         |             |        |       |  |

| Output Low Voltage                 | VOL          | VDD = 4.75V, ISINK = 1                  | .6mA              |         |             | 0.4    | V     |  |

| Output High Voltage                | Voн          | VDD = 4.75V, ISOURCE                    | = 1mA             | VDD - 1 |             |        | V     |  |

| Three-State Output Capacitance     | Cour         | (Note 5)                                |                   |         |             | 15     | ρF    |  |

# Multi-Range (±10V, ±5V, +10V, +5V), Single +5V, 12-Bit DAS with 8+4 Bus Interface

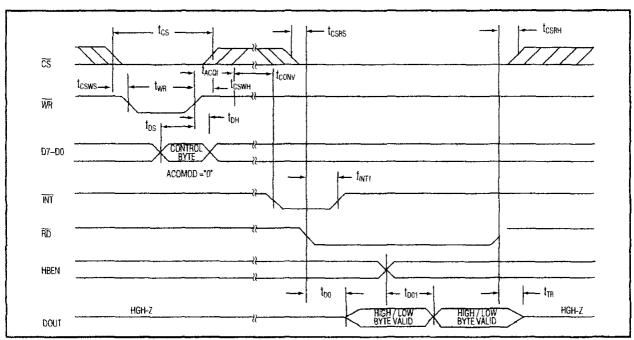

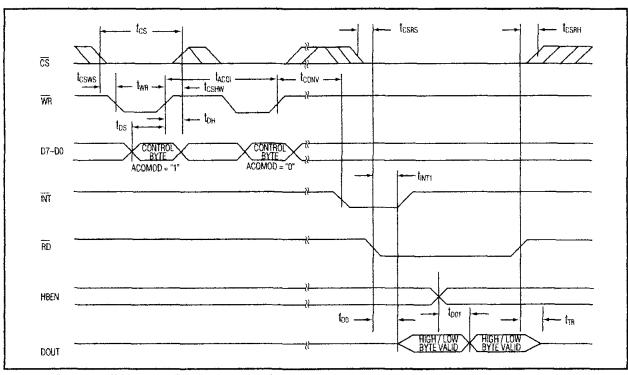

# TIMING CHARACTERISTICS

$(V_{DD} = 5V \pm 5\%; unipolar/bipolar range; external reference mode, V_{REF} = 4.096V; 4.7\mu F at REF pin; external clock, fCLK = 2.0MHz with 50% duty cycle; TA = TMIN to TMAX, unless otherwise noted.)$

| PARAMETER                                | SYMBOL | CONDITIONS                                 | MIN | TYP | MAX | UNITS |

|------------------------------------------|--------|--------------------------------------------|-----|-----|-----|-------|

| CS Pulse Width                           | tcs    |                                            | 80  |     |     | ns    |

| WR Pulse Width                           | twr    |                                            | 80  |     |     | ns    |

| CS to WR Setup Time                      | tcsws  |                                            | 0   |     |     | ns    |

| CS to WR Hold Time                       | tcswh  |                                            | ٥   |     |     | ns    |

| CS to RD Setup Time                      | tcsrs  |                                            | 0   |     |     | ns    |

| CS to RD Hold Time                       | tcsrh  |                                            | 0   |     |     | ns    |

| CLK to WR Setup Time                     | tcws   |                                            |     |     | 100 | ns    |

| CLK to WR Hold Time                      | tcwh   |                                            |     |     | 50  | ns    |

| Data Valid to WR Setup                   | tos    |                                            | 60  |     |     | ns    |

| Data Valid to WR Hold                    | tDH    |                                            | 0   |     |     | ns    |

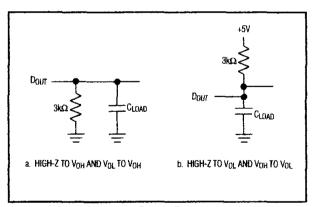

| RD Low to Output Data Valid              | †DQ    | Figure 2, C <sub>L</sub> = 100pF (Note 12) |     |     | 120 | ns    |

| HBEN High or HBEN Low to<br>Output Valid | tD01   | Figure 2, C <sub>L</sub> = 100pF (Note 12) |     |     | 120 | ns    |

| RD High to Output Disable                | İTR    | (Note 13)                                  |     |     | 70  | ns    |

| RD Low to INT High Delay                 | tint1  |                                            |     |     | 120 | ns    |

- Note 1: Accuracy specifications tested at V<sub>DD</sub> = 5.0V. Performance at power-supply tolerance limits guaranteed by Power-Supply Rejection test. Tested for the ±10V input range.

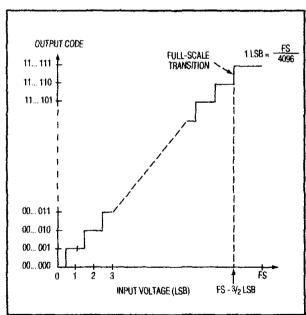

- Note 2: External reference: VREF = 4.096V, offset error nulled, ideal last code transition = FS 3/2LSB.

- Note 3: Ground "on" channel; sine wave applied to all "off" channels.

- Note 4: Maximum full-power input frequency for 1LSB error with 10ns jitter = 3kHz.

- Note 5: Guaranteed by design. Not tested.

- Note 6: Use static loads only.

- Note 7: Tested using internal reference.

- Note 8: PSRR measured at full-scale.

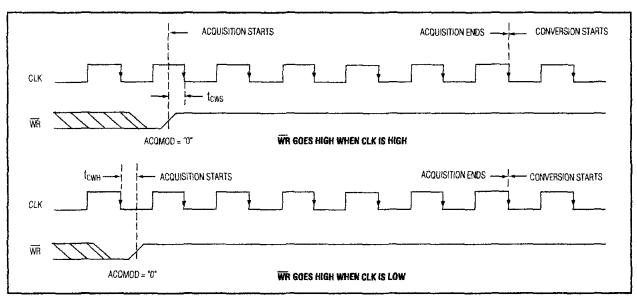

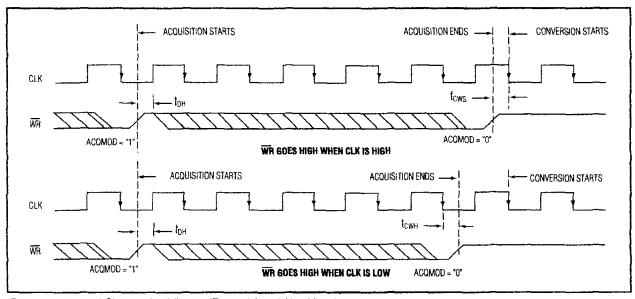

- Note 9: External acquisition timing: starts at data valid at ACQMOD = low control byte; ends at rising edge of WR with ACQMOD = high control byte.

- Note 10: Not subject to production testing. Provided for design guidance only.

- Note 11: All input control signals specified with tR = tF = 5ns from a voltage level of 0.8V to 2.4V.

- Note 12: tpp and tpp1 are measured with the load circuits of Figure 2 and defined as the time required for an output to cross 0.8V or 2.4V.

- Note 13: ttp is defined as the time required for the data lines to change by 0.5V.

# Multi-Range (±10V, ±5V, +10V, +5V), Single +5V, 12-Bit DAS with 8+4 Bus Interface

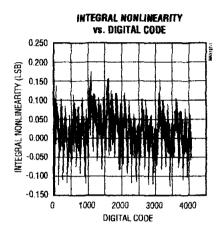

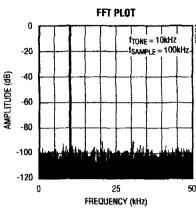

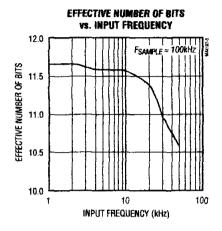

# Typical Operating Characteristics

$(T_A = +25^{\circ}C)$ , unless otherwise noted.)

# 4.090 4.095 4.090 4.080 AVERAGE (VREF) VS. TEMPERATURE 4.100 4.095 AV = 1.6384 REFERENCE REFADJ

TEMPERATURE (°C)

-35 -15 5 25 45 65

# Multi-Range (±10V, ±5V, +10V, +5V), Single +5V, 12-Bit DAS with 8+4 Bus Interface

# Pin Description

| PIN   | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CLK     | Clock Input. In external clock mode, drive CLK with a TTL/CMOS compatible clock. In internal clock mode, place a capacitor from this pin to ground to set the internal clock frequency; fclk = 1.56MHz typical with Cclk = 100pF.                                                                                                                                                                          |

| 2     | CS      | Chip Select, active low.                                                                                                                                                                                                                                                                                                                                                                                   |

| 3     | WR      | When $\overline{CS}$ is low, in the internal acquisition mode, a rising edge on $\overline{WR}$ latches in configuration data and starts an acquisition plus a conversion cycle. When $\overline{CS}$ is low, in the external acquisition mode, the first rising edge on $\overline{WR}$ starts an acquisition and a second rising edge on $\overline{WR}$ ends acquisition and starts a conversion cycle. |

| 4     | RD      | If $\overline{\text{CS}}$ is low, a falling edge on $\overline{\text{RD}}$ will enable a read operation on the data bus.                                                                                                                                                                                                                                                                                   |

| 5     | HBEN    | Used to multiplex the 12-bit conversion result. When high, the 4 MSBs are multiplexed on the data bus; when low, the 8 LSBs are available on the bus.                                                                                                                                                                                                                                                      |

| 6     | SHON    | Shutdown. Puts the device into full power-down (FULLPD) mode when pulled low.                                                                                                                                                                                                                                                                                                                              |

| 7–10  | D7-D4   | Three-State Digital I/O                                                                                                                                                                                                                                                                                                                                                                                    |

| 11    | D3/D11  | Three-State Digital I/O. D3 output (HBEN = low), D11 output (HBEN = high).                                                                                                                                                                                                                                                                                                                                 |

| 12    | D2/D10  | Three-State Digital I/O. D2 output (HBEN = low), D10 output (HBEN = high).                                                                                                                                                                                                                                                                                                                                 |